Цель

работы:

изучение

схемотехники цифровых шифраторов.

Оборудование:

Multisim

2001

Введение

Шифратором

или кодером (encoder) обычно называют

устройство, преобразующее унарный

позиционный код, получаемый от клавиатуры,

в какую либо разновидность двоичного

кода. Классический шифратор имеет М

входов и N выходов, и при

подаче активного сигнала на один из

входов (обязательно на один, и не более)

на выходе появляется параллельный

двоичный или, или иной параллельный

код, указывающий на номер возбужденного

входа.

Рис. Общая схема шифратора

Если

шифратор выполнен в виде отдельной

микросхемы, то на схеме он обозначается

следующим образом:

Приоритетный

шифратор

Приоритетные

шифраторы выполняют более сложную

операцию. При работе ЭВМ и в других

устройствах часто решается задача

определения приоритетного претендента

на пользование каким-либо ресурсом.

Несколько конкурентов выставляют свои

запросы на обслуживание, которые не

могут быть удовлетворены одновременно.

Нужно выбрать того, кому предоставляется

право первоочередного обслуживания.

Простейший вариант решения указанной

задачи — присвоение каждому источнику

запросов фиксированного приоритета.

Например, группа из восьми запросов

R7—R0 (R

от англ. request)

формируется так, что высший приоритет

имеет источник номер семь,

а далее приоритет уменьшается от номера

к номеру. Самый младший приоритет у

нулевого источника — он будет обслуживаться

только при отсутствии

всех других запросов. Если имеются

одновременно несколько запросов,

обслуживается запрос с наибольшим

номером.

Приоритетный

шифратор вырабатывает на выходе двоичный

номер старшего запроса.

Легко видеть, что

при наличии всего одного возбужденного

входа приоритетный

шифратор работает так же, как и двоичный.

Поэтому в сериях элементов двоичный

шифратор как самостоятельный элемент

может отсутствовать. Режим

его работы — частный случай работы

приоритетного шифратора.

В промышленных

сериях элементов имеются приоритетные

шифраторы для восьмиразрядных

и десятиразрядных слов. Функционирование

их отображается в таблице.

Таблица

|

EI |

R7 |

R6 |

R5 |

R4 |

R3 |

R2 |

R1 |

R0 |

а2 |

a1 |

a0 |

G |

E0 |

|

1 |

1 |

X |

X |

X |

X |

X |

X |

X |

1 |

1 |

1 |

1 |

0 |

|

1 |

0 |

1 |

X |

X |

X |

X |

X |

X |

1 |

1 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

X |

X |

X |

X |

X |

1 |

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

X |

X |

X |

X |

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

1 |

X |

X |

X |

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

X |

X |

0 |

1 |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

X |

0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

X |

X |

X |

X |

X |

X |

X |

X |

0 |

0 |

0 |

0 |

0 |

Таблица полностью характеризует работу

приоритетного шифратора при всех

возможных комбинациях сигналов: EI

— сигнала разрешения работы

данного шифратора; Е0 — сигнала,

вырабатываемого на выходе данного

шифратора при

отсутствии запросов на его входах для

разрешения работы следующего

(младшего) шифратора при наращивании

размерности шифраторов; G

— сигнала, отмечающего наличие запросов

на входе данного шифратора; R7—R0

— запросов на входах шифратора; а2—

a0

— значений разрядов выходного

двоичного кода, формирующего номер

старшего запроса. Все перечисленные

сигналы формируются при условии EI

= 1 (работа шифратора разрешена). При

EI = 0 независимо от состояний

входов запросов все выходные сигналы

шифратора становятся нулевыми.

Наращивание размерности приоритетного

шифратора

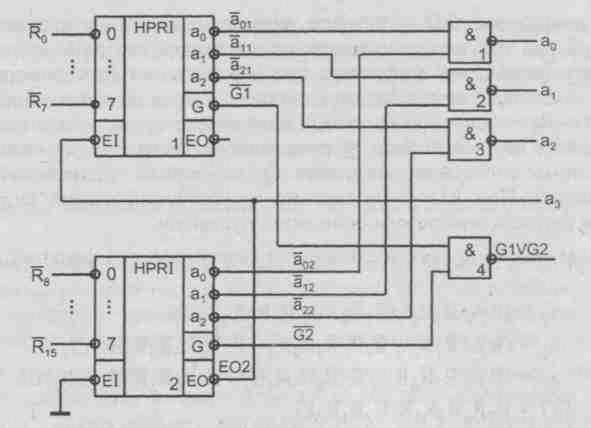

Условное обозначение

шифратора приоритета показано на рис.,

на котором изображено наращивание

числа входов запросов вдвое (от 8 до 16).

При этом показаны шифраторы с инверсными

входами и выходами, как это свойственно

большинству серий элементов.

Шифратор 2 — старший по приоритету, его

работа всегда разрешена подачей нуля

на вход EI2. Если на входах

R8…R15

есть хотя бы один запрос, то разрешения

на работу младшего шифратора 1 нет (Е02

= 1). Выходы шифратора 1 пассивны, т. е.

имеют единичные значения. При этом

элементы И-НЕ с номерами

1, 2, 3 играют роль инверторов для сигналов

аi2

(i

= 0, 1, 2). Поэтому на выходах

a0,

а1,

а2

схемы в целом

формируются сигналы от нуля до семи в

зависимости от номера старшего

запроса в шифраторе 2, что вместе с

единицей на выходе Е02 дает номера от 8

до 15.

Рис. Схема наращивания размерности

приоритетного шифратора

Если на входах шифратора 2 запросов нет,

он разрешает работу младшего, вырабатывая

сигнал Е02 = 0, и приводит свои выходы a0,

а1,

а2 в пассивное

единичное состояние. Теперь на выходы

а, схемы в целом передаются инвертированные

значения выходов a01,

а11,

а21

младшего шифратора, что вместе с

нулем в разряде а3

соответствует номерам от нуля до семи.

Таким образом, строится схема с 16 входами

запросов, причем вход R15

имеет старший приоритет. Выход элемента

4 принимает единичное значение при

наличии хотя бы

одного запроса в любом из шифраторов и

может использоваться как сигнал

запроса на прерывания для процессора

с последующим указанием процессору

номера старшего запроса.

Двоично-десятичное

кодирование

Если

каждый разряд десятичного числа

представить двоичным эквивалентом, то

результат получим в виде кода, который

называется двоично-десятичным кодом.

Так как десятичный разряд может быть

равен 9, требуется четыре бита, чтобы

закодировать каждый разрыд (двоичный

код для 9 равен 1001).

8

7 4 (десятичный

код)

1000

0111 0100 (двоично-десятичный

код)

Двоично-десятичный

код, таким образом, представляет каждый

разряд десятичного числа четырехбитовым

двоичным числом. При этом используются

только числа от 0000 до 1001. Двоично-десятичный

код не использует числа 1010, 1011, 1100, 1101,

1110 и 1111. Другими словами, применяются

только 10 из 16 возможных четырехбитовых

групп двоичного кода. Если вдруг в

машине, работающей с двоично-десятичным

кодом, каким-то образом появляется одно

из таких «запрещенных» чисел, то обычно

выдается сообщение об ошибке.

ПРАКТИЧЕСКОЕ

ЗАДАНИЕ

-

Разработайте

и реализуйте в Multisim 2001

схему шифратора в соответствии с одной

из приведенных таблиц истинности,

используя предложенный набор логических

элементов; (S0-S3 — входные переменные,

Q0-Q1, C — выходные).

Таблица A

|

А3 |

А2 |

А1 |

А0 |

Q1 |

Q0 |

C |

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

0 |

0 |

0 |

1 |

1 |

1 |

0 |

|

0 |

0 |

1 |

0 |

1 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

Таблица B

|

А3 |

А2 |

А1 |

А0 |

Q1 |

Q0 |

C |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

1 |

1 |

Таблица

A

|

А3 |

А2 |

А1 |

А0 |

Q1 |

Q0 |

C |

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

1 |

|

1 |

1 |

0 |

1 |

0 |

1 |

1 |

|

1 |

0 |

1 |

1 |

1 |

0 |

1 |

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

Таблица B

|

А3 |

А2 |

А1 |

А0 |

Q1 |

Q0 |

C |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

1 |

1 |

1 |

0 |

1 |

1 |

0 |

|

1 |

1 |

0 |

1 |

1 |

0 |

0 |

|

1 |

0 |

1 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

1 |

0 |

0 |

0 |

-

Разработайте

и реализуйте в Multisim 2001

схему приоритетного шифратора 4:2,

преобразующего десятичный код в

двоично-десятичный, с приоритетом

старшего разряда в соответствии с

приведенной таблицей истинности

(активный уровень 0), используя предложенный

набор логических элементов.

Таблица Е

|

А3 |

А2 |

А1 |

А0 |

Q1 |

Q0 |

С |

|

0 |

Х |

Х |

Х |

0 |

0 |

0 |

|

1 |

0 |

Х |

Х |

0 |

1 |

0 |

|

1 |

1 |

0 |

Х |

1 |

0 |

0 |

|

1 |

1 |

1 |

0 |

1 |

1 |

0 |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

-

Воспользовавшись

приведенным теоретическим материалом,

аналогично реализуйте Multisim

2001 схему увеличения разрядности

шифратора 8:3 до 16:4, используя микросхемы

74148N, 74LS148N(D),

74LS348N(D),

74HC148N(DW),

4532BT(BP).

КОНТРОЛЬНЫЕ

ЗАДАНИЯ

-

По заданию

преподавателя выполните преобразования

между двоичными, десятичными, восьмеричными

и шестнадцатеричными числами. -

Запишите

логические выражения, описывающие

работу собранной схемы. -

Нарисуйте

схему диодного шифратора для Вашей

таблицы истинности. -

Разберитесь

в схеме интегрального приоритетного

шифратора К555ИВ1 (74148):

-

Разберитесь

в схеме 16-входового приоритетного

шифратора, составленного из двух

микросхем 74148 (схема взята из документации

на 74F148 фирмы MOTOROLA):

Соседние файлы в папке цифровая электроника

- #

- #

- #

- #

- #

- #

Автор: • Июнь 7, 2020 • Лабораторная работа • 280 Слов (2 Страниц) • 618 Просмотры

Страница 1 из 2

лабораторная работа №6

ИССЛЕДОВАНИЕ ШИФРАТОРОВ И ДЕШИФРАТОРОВ

Цель работы: ознакомиться с принципами построения и функционирования шифраторов и дешифраторов, провести исследование этих схем, приобрести навыки схемотехнического моделирования на персональных компьютерах.

Задание 1. Построить схему и исследовать полный шифратор, преобразующий трехразрядный распределительный код в двоичный позиционный.

1.1 Таблица истинности полного шифратора:

|

Входы |

Выходы |

|||||||||

|

X7 |

X6 |

X5 |

X4 |

X3 |

X2 |

X1 |

X0 |

Y2 |

Y1 |

Y0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

Записываем выражения для функций выходов:

[pic 1]

Реализуем данные функции на элементах ИЛИ.

1.2 Собираем в программе MultiSim схему шифратора. Запускаем моделирование, по пробникам и цифровому индикатору убеждаемся, что схема функционирует в соответствии с таблицей истинности.

[pic 2]

Задание 2. Построить схему и исследовать приоритетный шифратор 4[pic 3]2.

2.1 Таблица истинности приоритетного шифратора 4[pic 4]2:

|

№ набора |

Входы |

Выходы |

||||

|

X3 |

X2 |

X1 |

X0 |

Y1 |

Y0 |

|

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

0 |

0 |

1 |

× |

0 |

1 |

|

2 |

0 |

1 |

× |

× |

1 |

0 |

|

3 |

1 |

× |

× |

× |

1 |

1 |

Функции выходов:

…

Доступно только на Essays.club

|

|

|

|

ПРАВИЛА РАЗДЕЛА «Электроника и схемотехника»

В дополнение к основным ПРАВИЛАМ ФОРУМА :

1. Не забывайте указывать полное наименование, модель,марку, изготовителя и краткие характеристики оборудования.

2. Аргументируйте свое мнение — приводите развернутое высказывание или источник информации.

3. Запрещается обсуждать, размещать запросы и ссылки на схемы и оборудование

конфликтующие с законом или несущие явную потенциальную угрозу применения.

4. Не разрешается давать советы из разряда «Выкинь это старьё» и подобные.

5.Наглая реклама и самопиарщиана подлежит отстрелу сопровождаемому соответстующим наказанием

6.Запрещается создавать темы с просьбой выполнить какую-то работу за автора темы.

Форум является средством общения и общего поиска решения. Вашу работу за Вас никто выполнять не будет.

7.Запрещается создание тем, не относящиеся непосредственно к «Электронике и схемотехнике»

8.В этом разделе КАТЕГОРИЧЕСКИ запрещен мат во всех его проявлениях, а также: Ругань, оскорбления, переход на

личности.

Если Вы увидели нарушение правил раздела или форума, не поленитесь сообщить об этом модератору.

Участники форума, нарушающие правила, будут наказываться, а вносящие вклад в развитие форума — награждаться (DigiMoney и прочими радостями).

Приятного вам общения!

Моделирование шифратора в multisim

, Транзисторный шифратор 10 в 8

- Подписаться на тему

- Сообщить другу

- Скачать/распечатать тему

|

|

|

|

Рейтинг (т): 1 |

Здравствуйте. Очень нужна помощь. Никак не могу сообразить, как смоделировать шифратор на биполярных транзисторах из 10-ной в 8-ную в multisim. Помогите пожалуйста |

|

simsergey |

|

|

А что именно не получается? |

|

heyleech |

|

|

Рейтинг (т): 1 |

Скажем так, я не понимаю, как это нужно сделать |

|

simsergey |

|

|

А задание есть? Обычно в нем можно найти подсказку. Вообще, задание зверское, если честно. Нам таких никогда не попадалось. Скорее всего нужно: Я не знаю что у Вас в задании, по сложности тянет на курсач или диплом. |

|

heyleech |

|

|

Рейтинг (т): 1 |

Проектное задание. Мне просто сказали :»Тебе нужно смоделировать шифратор, который будет переводить из 10-ной системы в 8-ную, на биполярных транзисторах» и всё, никаких подсказок и напутствий Добавлено 31.10.16, 18:08 |

|

heyleech |

|

|

Рейтинг (т): 1 |

simsergey Прикреплённая картинка

|

|

simsergey |

|

|

heyleech, начало хорошее. Транзисторы, простыми словами, — это устройства, похожие на ключи, которые в зависимости от поданного напряжения (или втекающего тока) на базу, относительно эмиттера (база-эмиттер) открываются, т.е. пропускают в процентном отношении ток через коллектор к эмиттеру (коллектор-эмиттер). Благодаря такому свойству их используют в логических элементах, рассчитывая схемы. — это уже электроника. После — спрашивайте дальше, подскажем Если понадобится, могу поделиться методиками расчета логических элементов. Расчетов много… Сообщение отредактировано: simsergey — 31.10.16, 19:45 |

|

heyleech |

|

|

Рейтинг (т): 1 |

simsergey Да, если вам не сложно поделитесь расчётами ) Прикреплённая картинка

|

|

simsergey |

|

|

Уже что-то)) Из интересного, думаю, стоит добавить, что в виртуальном мире логических элементов различают ‘1’ и ‘0’, а в электронике это реализуется определенным уровнем напряжений. Например, на схеме ниже ‘0’ — 0.2 В, ‘1’ — 3.5 В. Но эти значения не устанавливаются точно, они плавают в некоторых пределах, поэтому на один элемент можно нагрузить только определенное количество элементов, иначе уровни могут смешиваться до чего-то среднего, что в результате для одних элементов может означать ‘1’, а для других ‘0’ одновременно, а это явно приводит к неработоспособности схемы. Посмотрите в сторону таких схем. До логических элементов ИЛИ-НЕ и И-НЕ потребуется небольшая доработка., принцип такой же как и Вашей схеме. Цитата heyleech @ 03.11.16, 13:15 simsergey Да, если вам не сложно поделитесь расчётами ) Смотрите личные сообщения. Сообщение отредактировано: simsergey — 04.11.16, 06:38 |

|

K313 |

|

|

Full Member Рейтинг (т): 9 |

Цитата heyleech @ 31.10.16, 18:01 шифратор, который будет переводить из 10-ной системы в 8-ную и где, интересно, у Вашей схемы вход 10-ной системы? |

|

simsergey |

|

|

Цитата K313 @ 09.11.16, 14:56 у Вашей схемы вход 10-ной системы?

смотря что называть 10-ой системой.. |

|

heyleech |

|

|

Рейтинг (т): 1 |

K313 Скорее всего, схема неправильная. Нигде не могу найти то, что мне нужно |

|

simsergey |

|

|

Смотрите картинку. Она отражает саму идею.

У Вас 10 входов и 8 выходов. Скорее всего, нужно составить «таблицу истинности», на основе нее составить «карты Карно». В этой схеме далее заменить элементы. Разрядность еще нужно знать, на картинке одноразрядный элемент. Одна цифра на входе. И да, я не хочу никого путать.. Вопрос изначально стоял сделать на транзисторах в мультисиме., у Вас точно должна быть реализация через жесткую логику? Или там ЦАП-АЦП элемент? Сообщение отредактировано: simsergey — 09.11.16, 18:41 |

|

K313 |

|

|

Full Member Рейтинг (т): 9 |

Цитата heyleech @ 09.11.16, 16:39 что мне нужно Прежде чем решать задачу, нужно сначало понять само задание. Когда определитесь, что у Вас на входе, и что у Вас на выходе должно быть, тогда и можно будет думать дальше…. |

|

heyleech |

|

|

Рейтинг (т): 1 |

K313 Задание звучало так : «Смоделировать шифратор из 10-ной системы в 8-ную систему на биполярных транзисторах» |

0 пользователей читают эту тему (0 гостей и 0 скрытых пользователей)

0 пользователей:

- Предыдущая тема

- Электроника и схемотехника

- Следующая тема

[ Script execution time: 0,0957 ] [ 19 queries used ] [ Generated: 29.05.23, 05:17 GMT ]

. Нет никаких примеров, по которым я бы смогла сообразить, как смоделировать такой шифратор

. Нет никаких примеров, по которым я бы смогла сообразить, как смоделировать такой шифратор