Пока наши соседи по цеху спорят о конкурентоспособности Эльбруса, я продолжаю идти к своей заветной цели — склепать свой

собственный Отечественный Процессор (TM)

. Ранее я рассказывал про программу, финансируемую Google, которая позволяет энтузиастам бесплатно получить прототип их разработок в кремнии. Если вы хотите увидеть всю подноготную процесса производства современных чипов, то этот туториал точно для вас!

Как разработать микросхему, от идеи до результата. Ссылки на все статьи։

В этой серии статьей мы раскроем всё: от получения документации до layout-а. Но перед этим давайте разберёмся, как вообще разрабатывают микросхемы.

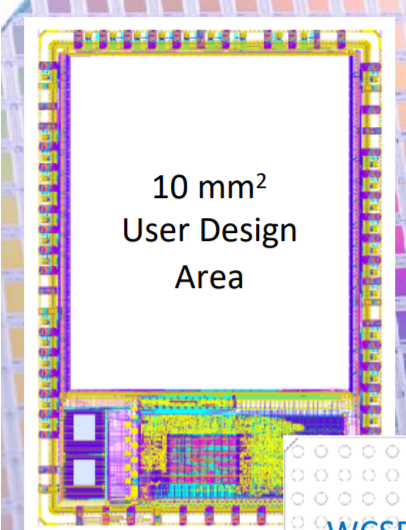

50 микросхем, бесплатно для всех проектов с открытым исходным кодом

Статья выходит очень вовремя, ведь в Декабре будет MPW-4 от SkyWater! У SkyWater было уже три производства микросхем по технологии Sky130, и очень даже успешных! Для желающих БЕСПЛАТНО есть возможность произвести вашу микросхему в количестве 50 штук. Для этого надо перейти на страницу MPW-4 от Efabless и зарегистрироваться, к сожалению, анонса на сайте пока нету, а регистрация на MPW-3 закончилась 15 ноября. Есть ещё несколько требований, например, ваша микросхема, должна быть с открытым исходным кодом, подробнее можно узнать, заглянув в анонс.

Вообще, мне удалось познакомиться с разработчиками и они очень классные люди! Спасибо комьюнити, и спасибо компаниям и странам, которые профинансировали просто отличный софт, с которым нам предстоит познакомиться в этой статье.

Спойлер։ Готовая схема NAND

Но ведь Sky130 не новая, так почему же сейчас вдруг выходит эта статья? Дело в том, что Sky130 имеет полностью открытую PDK, и это первая в мире технология, документация которой доступна для всех. Также примечательно то, что данная технология заставила Open Source комьюнити попотеть, ибо вместе с выходом технологии стали доступны KLayout и Magic VLSI, а команде Efabless удалось на основе OpenRoad сделать OpenLane для синтеза цифровых микросхем. Наряду с уже существующими NGSPICE и XSCHEM это позволяет разрабатывать полностью открытые микросхемы от идеи до готового продукта просто огромные проекты, возможности реально неограниченны (если вы уместите всё в 10 квадратных миллиметров).

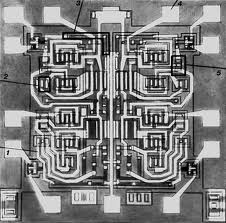

Микросхема изнутри

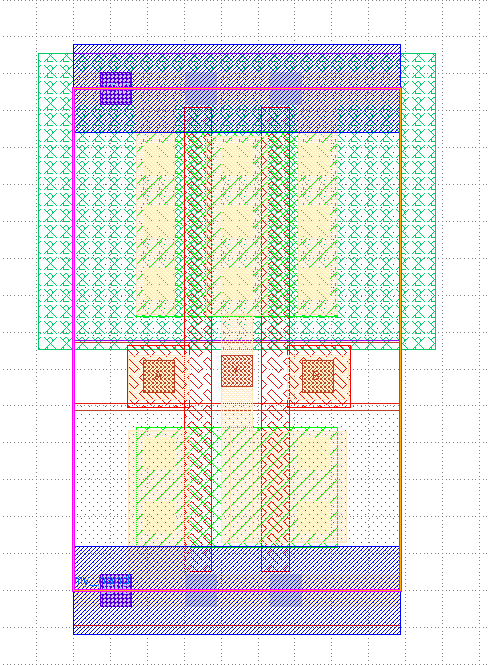

Все микросхемы состоят из подложки и корпуса. На корпусе находятся ножки, которые подключены к контактным площадкам подложки, используя специальные провода.

Иногда микросхемы делают по технологии Flip-Chip, которая не использует провода, вместо этого используются металлические контакты, которые напрямую подключены к верхним слоям металла внутри микросхемы.

Источник

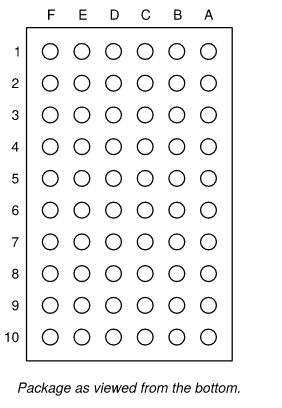

У sky130 есть возможность использовать корпус WCLSP 6×10:

Если вам захочется использовать другой корпус, для вас доступен ChipIgnite, всего за $9,999 вы можете получить 100 микросхем в корпусе QFN, либо 300 штук в корпусе WCSP. А за 1000 штук вы заплатите всего каких-то жалких двадцать киллобаксов.

Несмотря на корпус, который прямо-таки просится быть Flip-Chip, всё-таки нам доступен только WireBond. Вот оболочка, в которую нам предстоит интегрировать нашу схему։

▍ Подложки

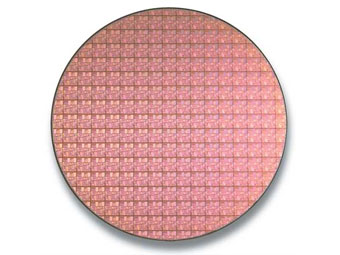

Кроме корпуса, внутри находится «сердце» микросхемы, подложка из кремния, в котором изготовлены наши транзисторы, слои металла и изоляции. Именно кремний определяет функциональность нашей микросхемы, и в мире существуют несколько компаний, производящих этот самый «кремний».

Для того чтобы эта компания могла произвести вашу микросхему, эту самую микросхему нужно сначала разработать, а затем только передать её в производство. Для этого используется стандарт файлов GDS-II, либо другие стандарты. GDS-II является многослойной векторной картинкой, которая соответствует требованиям этой самой компании. Но как нам узнать, какие файлы соответствуют этим требованиям или нет? Здесь на помощь приходит так называемый Process Design Kit или PDK.

Пример микросхемы по технологии sky130: ускоритель расчёта SHA3․

Process Design Kit

Process Design Kit содержит следующие компоненты:

- Технологическая документация. Этот файл содержит на удобно перевариваемом формате описание и требования к конечному файлу, кроме того, эта документация содержит примеры и описания транзисторов. Для sky130 документацию можно найти тут

- Модели для симуляции элементов схемы в формате SPICE. Эти модели используются для симуляции компонентов интегральной схемы. Перед тем как нарисовать структуру кремния, вам нужно сначала определиться со схемой, которую вы будете рисовать. Эти модели можно найти на гитхабе гугла.

- Технологические файлы, которые позволяют связать файл GDS-II и слои при производстве. Для Magic/Klayout эти файлы можно найти на гитхабе Open_PDKs

- Библиотека примитивов — Транзисторов, резисторов, конденсаторов и так далее для схематического представления, которые можно найти на гитхабе

- Правила Design Rule Check. Эти файлы привязаны к конкретному программному обеспеченью и содержат список правил, на которые в автоматическом режиме будут проверяться ваши интегральные схемы или её отдельные компоненты.

- Parasitic Extraction rules или правила описывающие паразитические свойства. Эти правила позволяют просчитать паразитные конденсаторы, индукторы и резисторы. После PEX

сгенерированный netlist содержит паразитные конденсаторы и резисторы, а сам netlist используется чтобы произвести симуляцию компонентов как можно более приближённой к реальной интегральной схеме. - Layout versus Schematic check или правила, которые позволяют получить из вашего GDS-II так называемый netlist. После чего его можно сравнить со схемой, которую вы нарисовали и уже просимулировали. DRC/PEX/LVS правила для Magic можно найти на гитхабе Open_PDKs

Skywater 130nm

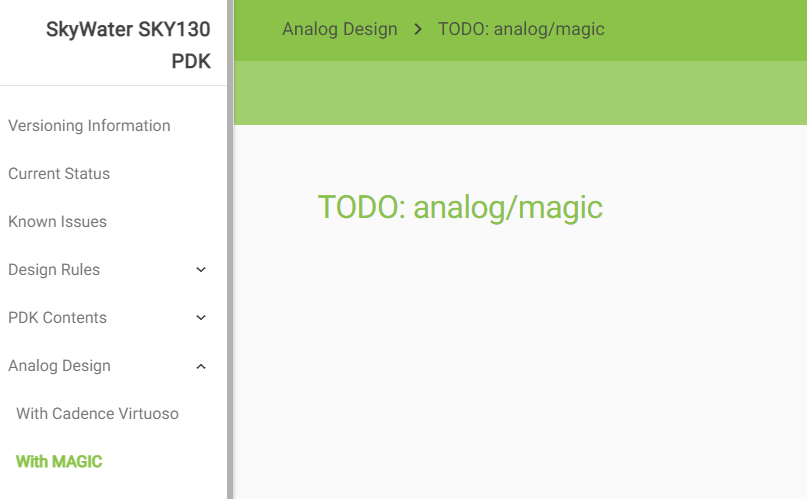

Для этого давайте сначала разберём, что нам предоставил Skywater/Google для разработки микросхемы по технологии SKY130. Гуглим SKY130 и кроме кучки новостей, находим новость от efabless и офицальную документацию SKY130. Практически вся документации находится в виде ту-ду:

Тем не менее гуглим sky130 туториал и находим кучу всего, и все они неполные. К счастью, ваш покорный слуга не первый год в разработке интегральных схем, и поэтому я просто нашёл, как можно больше информации и решил всё расписать по частям в этой статье. Огромное количество информации найти нельзя, поскольку было получено лично от разработчиков в Slack канале sky130. Но перед тем как продолжить — немного теории.

Custom Design Flow

Custom Design Flow используется для того, чтобы разрабатывать аналоговые либо смешанные схемы. Custom Design Flow обладает наибольшей гибкостью, ибо позволяет разработать абсолютно любую схему, но её недостатком является долгий цикл разработки.

Custom Design Flow состоит из нескольких фаз, но при этом некоторые фазы повторяются, если результат не удовлетворяет требованиям. Вот эти фазы։

▍ Спецификация

Давайте разберём каждый шаг. Specification, который между разработчиками называется «спека», содержит в себе все необходимые требования к итоговой схеме. Иногда микросхема настолько большая, что её разделяют на более мелкие куски и распределяют по командам. Для того чтобы каждая команда знала, какую часть микросхемы нужно собрать, для этой команды составляется спецификация.

В спецификации часто содержится։ Рабочие напряжения, технология (например, sky130), требования к площади компонента, ограничения по слоям, функциональность и характеристики схемы. В этом материале мы будем разрабатывать простой NAND, но очевидно, что ячейки стандартной библиотеки содержат гораздо большее количество ячеек, чем простая NAND. Про это расскажу далее.

Пример спецификации к компоненту ввода вывода։

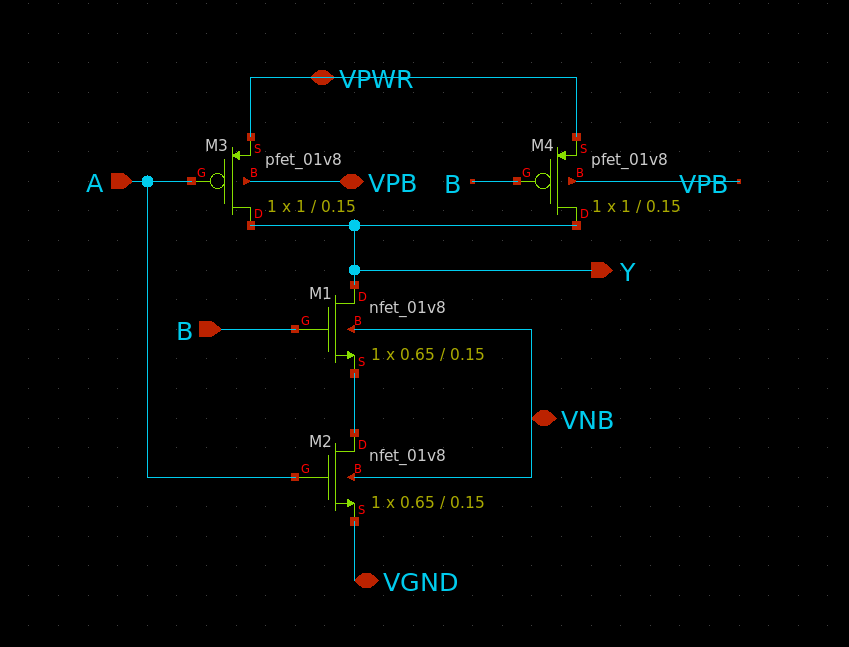

▍ Схемотехническое представление

Схемотехническое представление (schematic) это представление вашей микросхемы используя компоненты вашей технологии։ транзисторы, резисторы, конденсаторы, а также пины и их подключения. Схема составляется для двух целей։ проверить её работоспособность в идеальных условиях, когда сопротивление подключения и паразитные конденсаторы отсутствуют и понять, насколько мы близки к требованиям спецификации. Очевидно, что нам нужно оставить запас для паразитных ёмкостей и сопротивлений.

Пример схемотехнического представления։

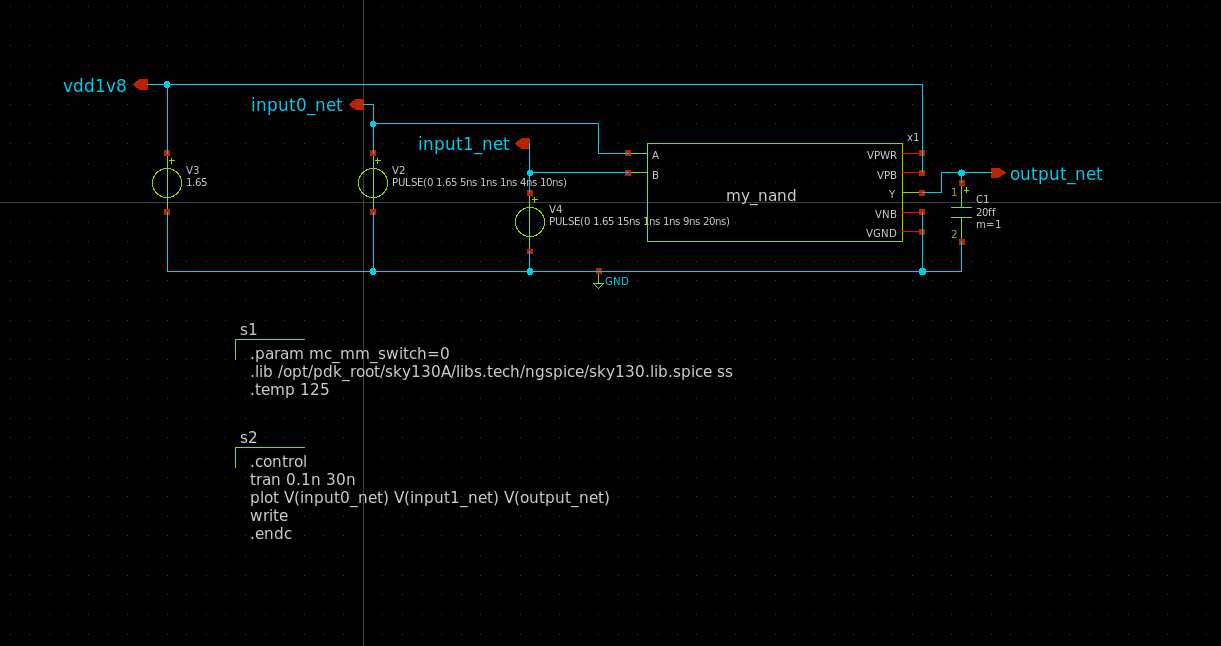

▍ Testbench

Testbench это схема, в которой вашим компонентам предстоит работать. У вас может быть бесконечное количество testbench, и подкомпонентов, и testbench-ов для этих подкомпонентов. Testbench используется для того, чтобы измерить необходимые характеристики. Про это будет далее.

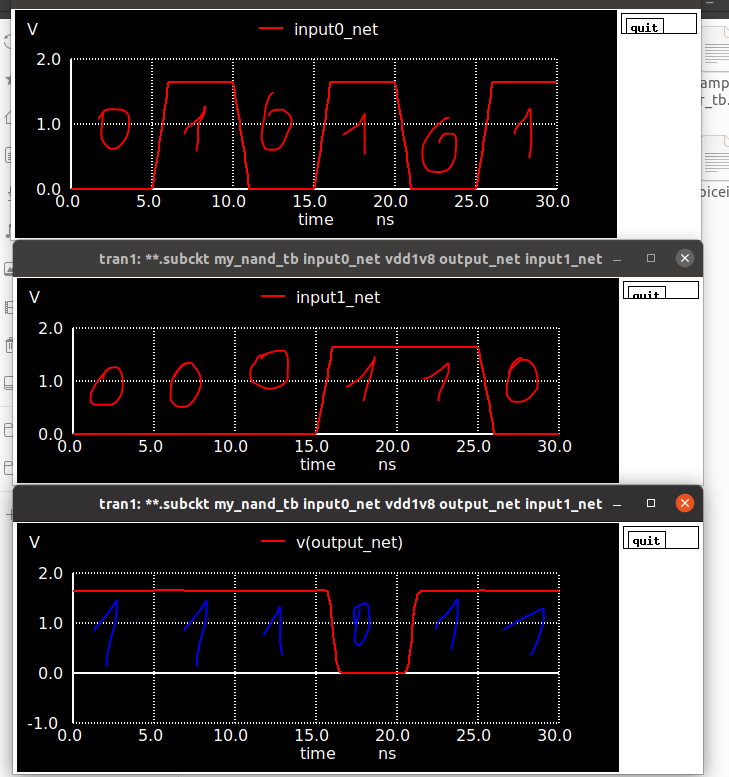

Пример testbench для NAND:

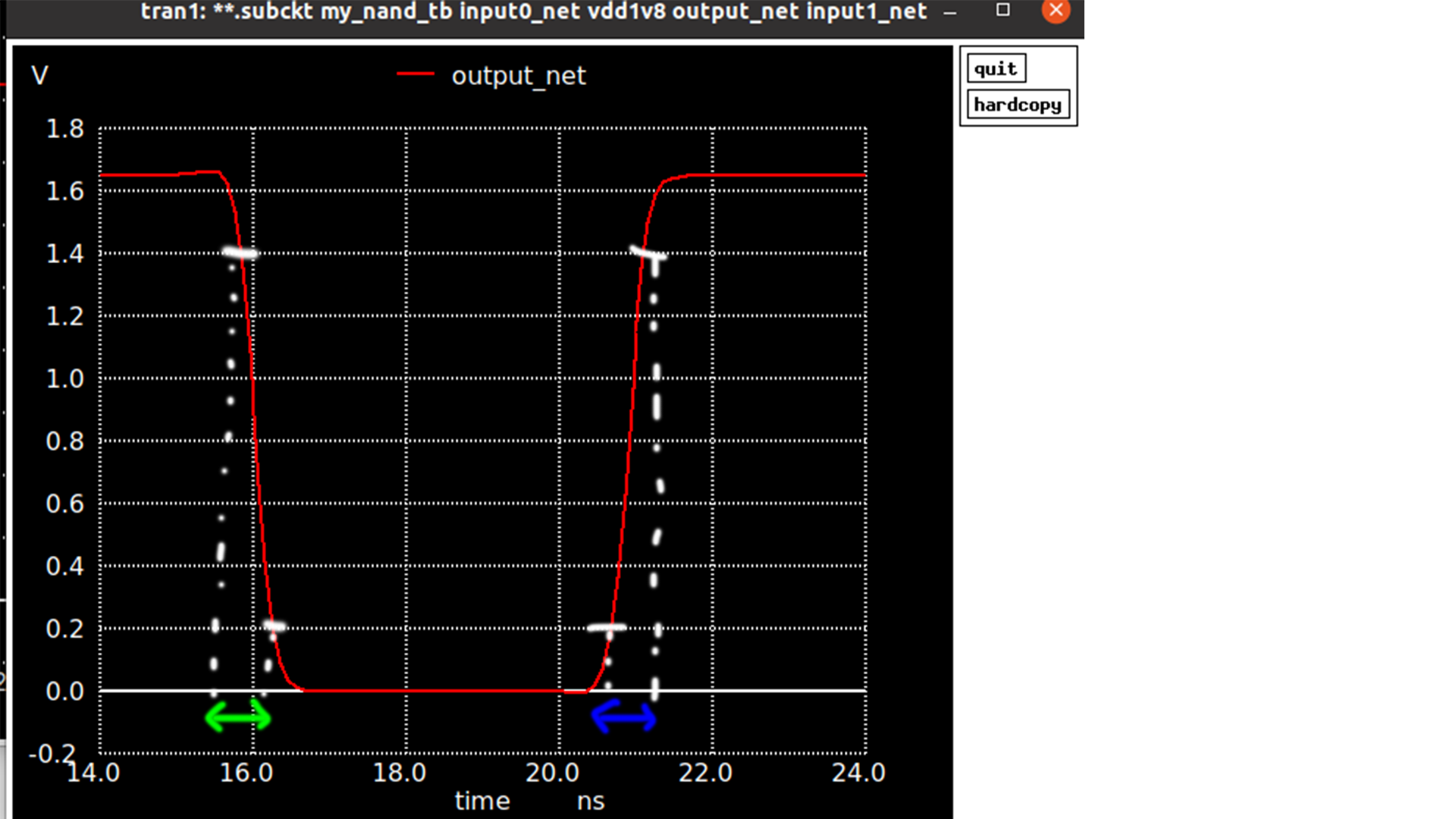

▍ Симуляция схематического представления.

Для того чтобы просимулировать схематическое представление и testbench конвертируется в netlist в формате SPICE. Для создания схематического представления я использовал XSCHEM и сгенерировал Netlist в формате SPICE на основе testbench, которое в свою очередь содержит определение нашей схемы.

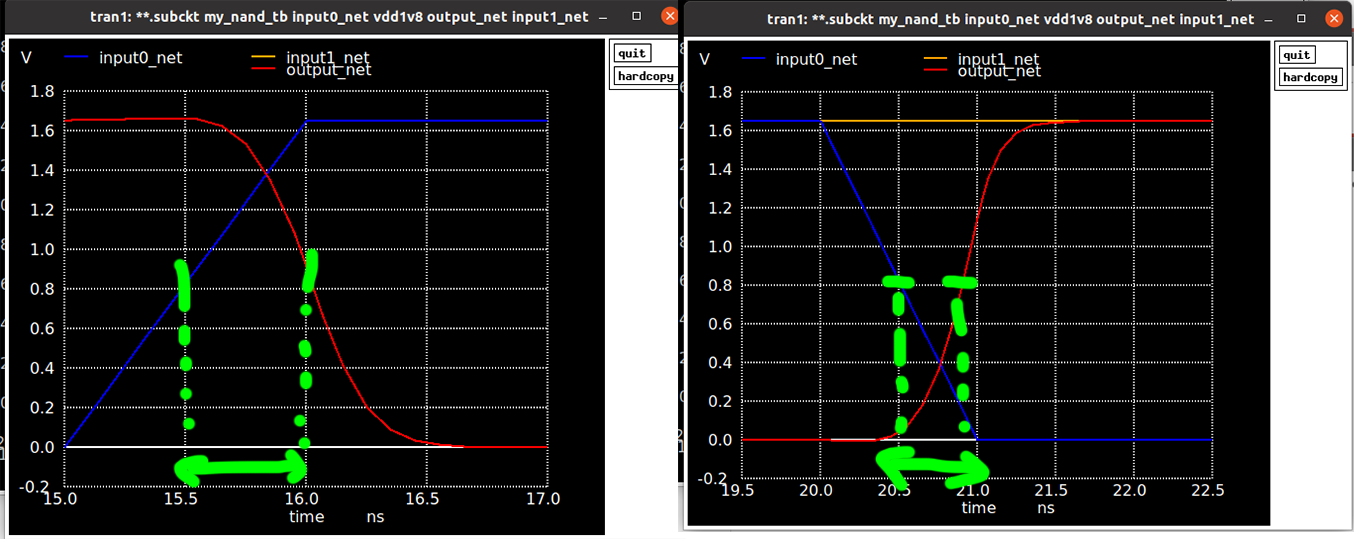

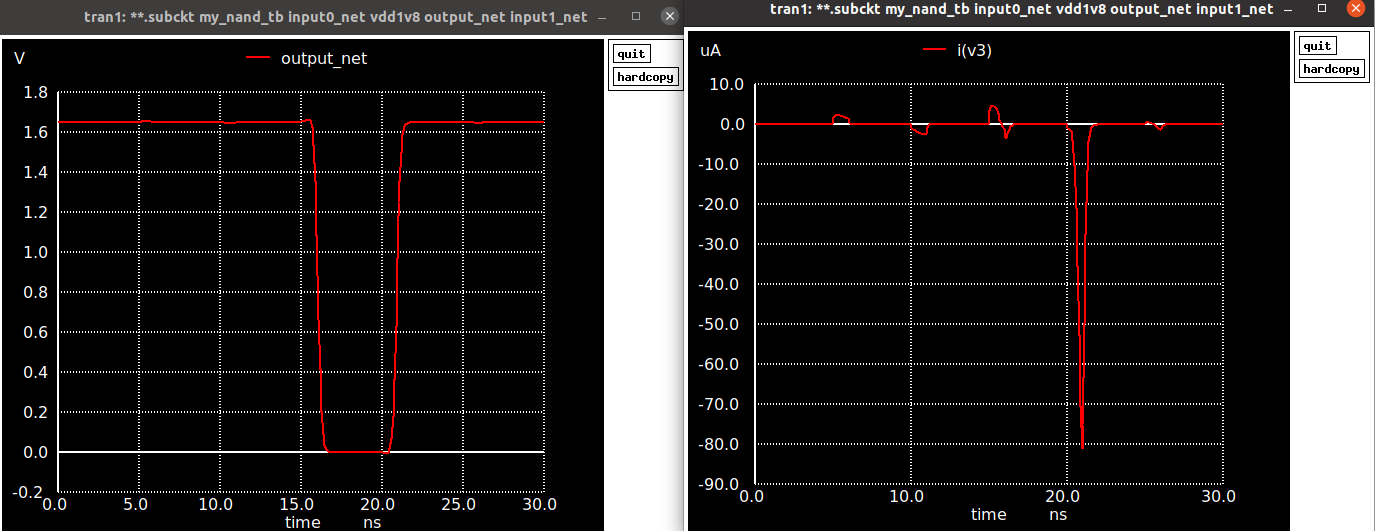

Затем я скормил Netlist симулятору NGSPICE, который посчитал все параметры, которые, мы выставим. Также, NGSPICE сгенерировал результат симуляции, который содержит значения напряжения и тока в зависимости от времени. Затем мы просим NGSPICE нарисовать нам графики зависимости напряжения на выходе и входе в зависимости от времени. А еще мы можем попросить NGSPICE провести любые измерения:

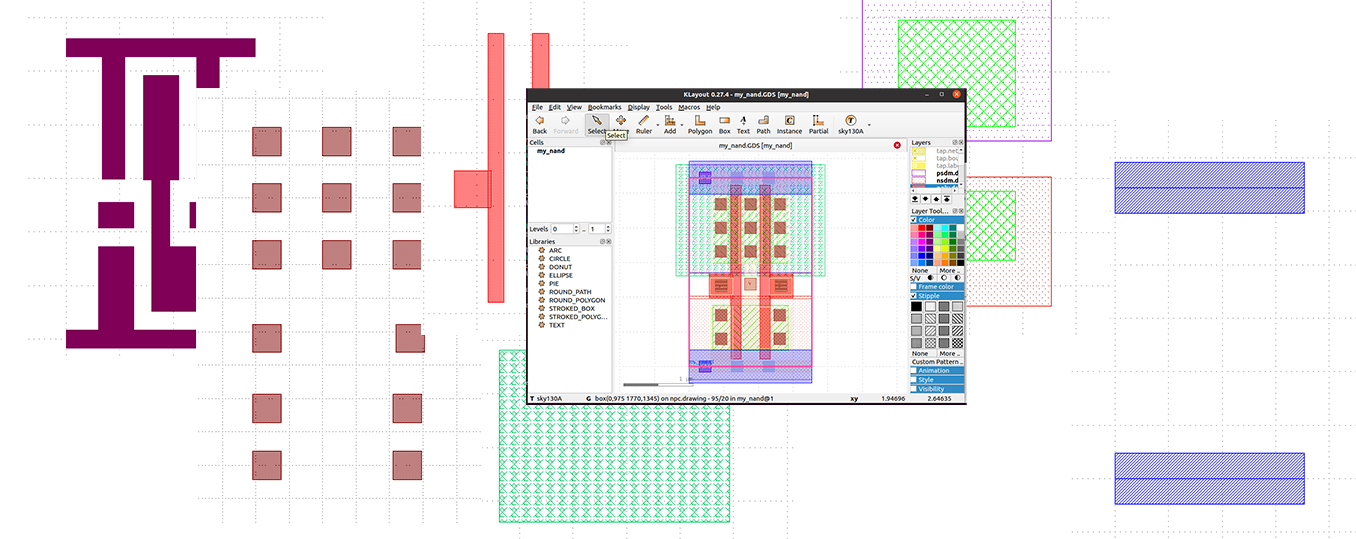

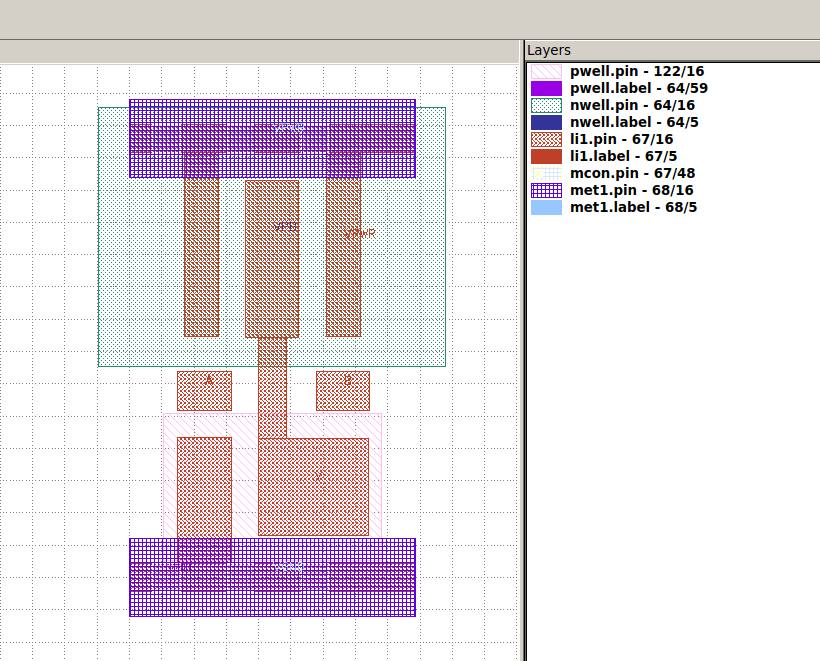

▍ Разработка Layout

Layout это такое представление, в котором, содержатся полигоны, которые будут нанесены на маску. Затем эта маска будет использоваться для того, чтобы создать диффузии, слои металла, и всё остальное! Magic VLSI и Klayout могут использоваться для создания GDS-II файлов, которые содержат полигоны и прочие примитивные объекты по типу текста. Мы будем использовать Klayout, поскольку у него значительно проще интерфейс.

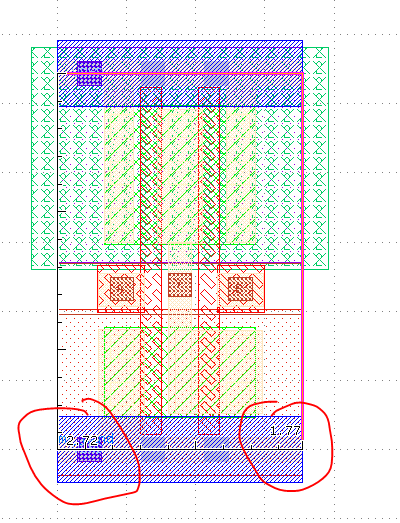

Пример, на картинке видны отдельные слои։ диффузий металла и межслойных соединений, а также всё в сборе:

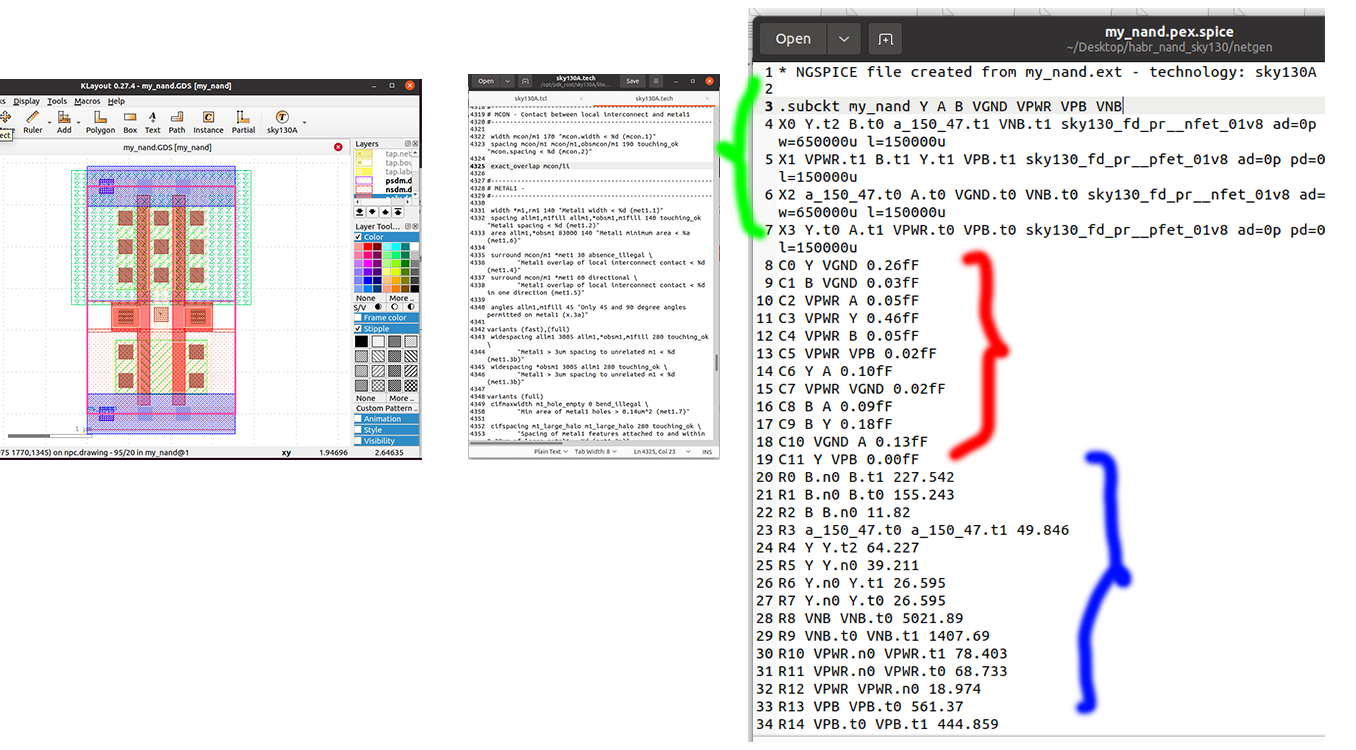

▍ Design Rule Check (DRC)

Design Rule Check используется для того, чтобы проверить маски на возможность произвести физическую микросхему. Представьте, что вы сделали металл очень тонким и если попробовать произвести по вашей микросхеме, то полученный металл будет слишком тонким, и во время производства он просто исчезнет. Это если маску вообще удастся сделать.

Для sky130 используется программа Magic VLSI, и правила, написанные именно под эту программу. Если вам захочется использовать что-то другое, то вам придётся написать эти правила уже под вашу программу.

После того как вы установите Open_PDKs по пути $PDK_ROOT/sky130A/libs.tech/magic/sky130A.tech, вы найдёте правила DRC для Magic. Используя именно эти правила Magic VLSI будет проверять ваш Layout.

На картинке видно, слева направо: Layout, правила Magic VLSI для sky130, результат проверки DRC.

Кликабельно

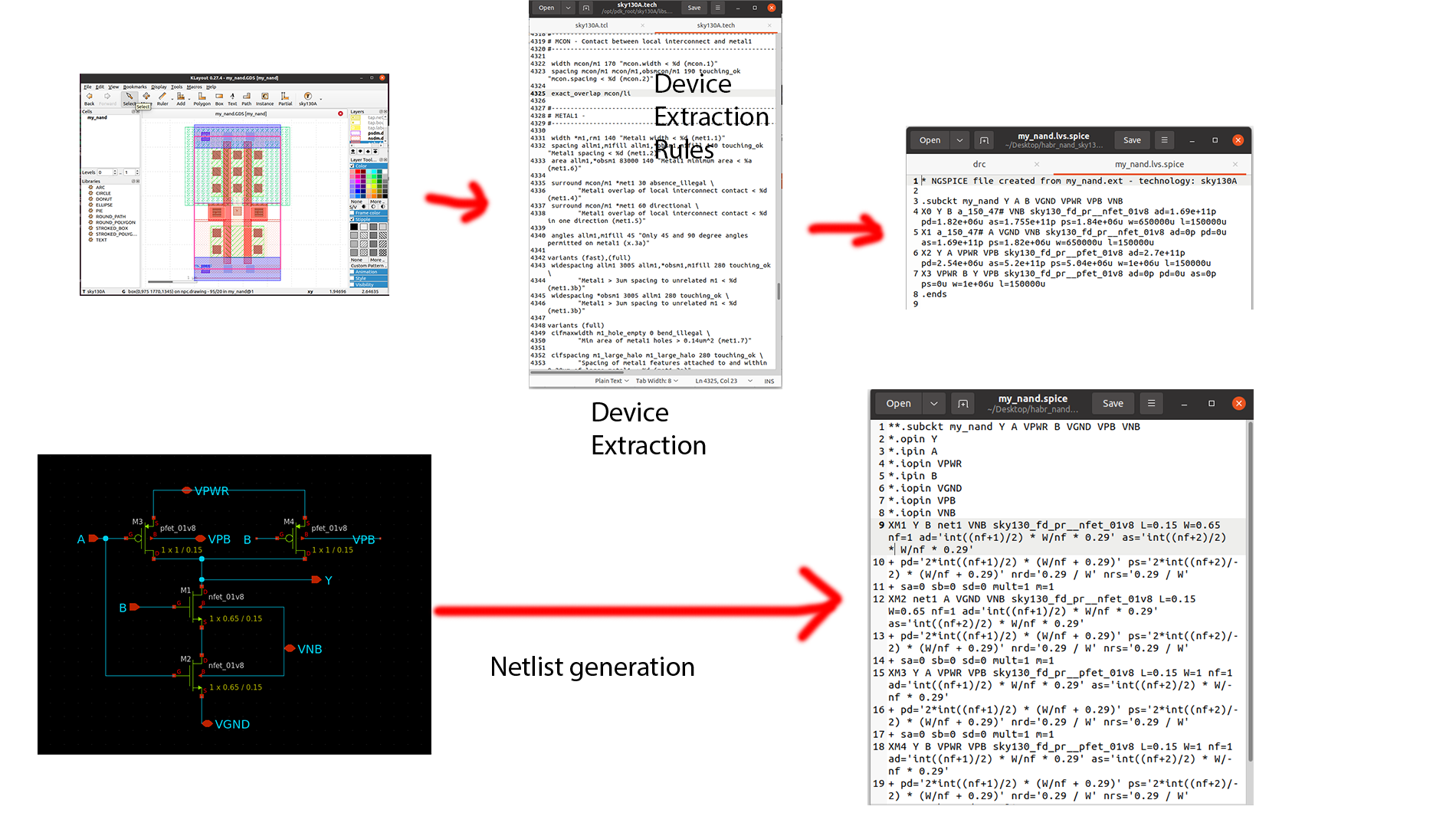

▍ Layout Versus Schematic (LVS)

Layout Versus Schematic используется для того, чтобы удостовериться, что разработанный Layout соответствует схематическому представлению. Это проверка сначала использует Layout и правила Device Extraction для того, чтобы получить схематическое представление, которое получится в результате производства данной микросхемы или компонента.

Мы будем использовать Magic VLSI для того, чтобы сгенерировать Netlist из Layout-а, затем сгенерированный Netlist сравнивается с Netlist-ом соответствующего компонента. Сначала сравниваются компоненты и их параметры: Транзисторы, резисторы, конденсаторы, затем сравниваются все подключения между ними и пинами компонента. Про это будет далее.

Если вы попробуете сравнить сгенерированный Netlist и Netlist-ом соответствующий компонент, скорее всего у вас будет ошибка, дело в том, что netgen не знает, что у транзисторов симметричный drain и source. Также, netgen не будет знать, о том, что транзисторы, подключённые так, чтобы все ножки были подключены друг к другу, можно объединить, суммировав параметр W.

Аналогично с последовательным подключением drain, source, если gate и bulk подключены аналогичной ножке других транзисторов, то эти транзисторы можно объединить, суммировав параметр L. Не нашёл информации об этом, чтобы правильно всё расписать, тем не менее решил упомянуть.

▍ Parasitics EXtraction (PEX)

Parasitics EXtraction похож на Device Extraction, но кроме компонентов и их подключений так же извлекаются паразитные конденсаторы и резисторы. Таким образом, получается модель для симуляции, максимально приближённая к готовой микросхеме. Для этого мы будем использовать Magic VLSI. Очевидно, чтобы Magic VLSI знал, характеристики металлов и других проводников, нужен технологический файл.

Слева направо, layout, правила паразитных ёмкостей и сопротивлений, и зеленным отмечены компоненты нашей схемы, красным паразитные ёмкости, синим паразитные сопротивления.

Digital Design Flow

В современном мире микросхем, вручную разработать и проверить микросхему практически невозможно из-за количества её компонентов. В этом плане нам помогает «поток разработки цифровых компонентов».

«Поток разработки цифровых компонентов» позволяет разрабатывать цифровые части микросхем, используя высокоуровневый язык, называемый Register Transfer Level, который позволяет разрабатывать по-настоящему огромные микросхемы. Всё — начиная от процессоров, ускорителей, ПЛИС и видеопроцессоров разрабатываются с использованием Register Transfer Level и Digital Design Flow, хотя они содержат очень много аналоговых или смешанных компонентов, цифровые компоненты занимают значительно бОльшую площадь, чем аналоговые.

Следующие шаги используются для разработки цифровых микросхем:

▍ Register Transfer Level (RTL)

Для того чтобы разработать цифровую микросхему используется RTL Verilog, который описывает регистры и изменения в этих самых регистрах. Используя регистры для хранения, ваш конечный продукт может запоминать информацию, например, сетевые пакеты, значение внутри вашего процессора или даже промежуточные результаты расчётов. Если хотите подробнее узнать про RTL Verilog, рекомендую прочитать книгу Харриса и Харриса, либо её перевод на русский, либо её полную версию на русском.

Пример, найти полную версию можно тут:

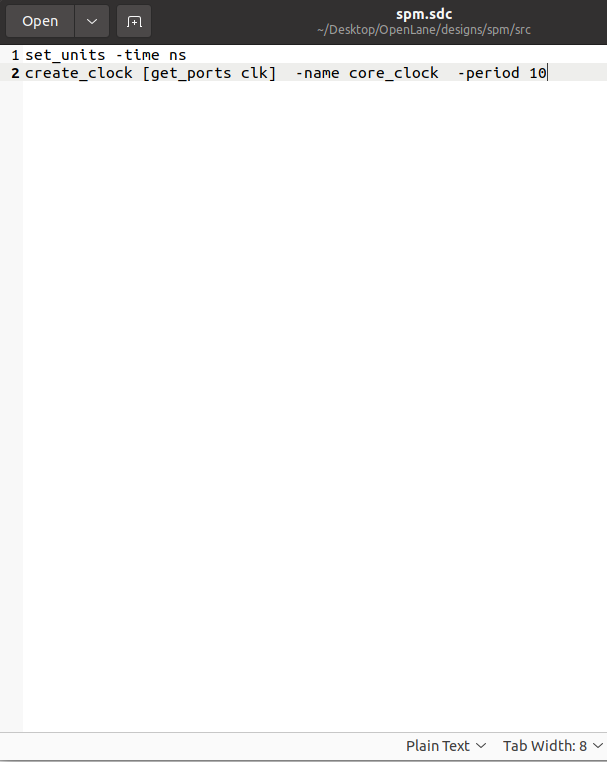

▍ Design Contraints

Поскольку RTL не предусматривает механизма описания информации:

- о временных характеристиках ввода и вывода

- о временных характеристиках регистров, вроде максимального и минимального количества тактов до поступления данных на вход регистра

- о характеристиках сигнала тактования, вроде частоты, изменения длинны единицы и нуля

- И другая информация вроде сигналов, задержки которых не имеют значения (квазистатичные сигналы)

То для этих целей используется Design Constraints, который обычно сделан в формате Synopsys Design Constraints (.sdc).

Простой пример, в котором объявлен только сигнал тактования и частота.

▍ Синтез

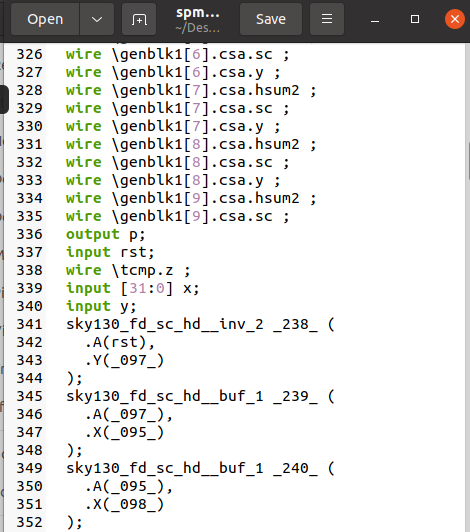

Синтез берёт на вход Design Constraints, RTL код и превращает его в представление из элементов стандартной библиотеки. Для этого стандартная библиотека, должна быть предварительно разработана. Библиотека стандартных ячеек (Standard Cell Library) содержит в себе один ключевой файл: .lib. Этот файл содержит информацию о задержке каждой ячейки, а также другие важные временные параметры, информацию о размере ячейки и потребление ячейки в разных состояниях. Инструмент синтеза выбирает ячейки и генерирует gate level netlist:

Также именно в этом шаге единицы и ноли, подключённые к входам компонентам, заменяются на Tie-Hi и Tie-Lo компоненты, поскольку прямое подключение входов ячеек к соединениям питания запрещено.

Для синтеза используется Yosys, который я использовал много раз, и он мне он очень понравился. Конечно, были небольшие проблемы, но никаких багов, ломающих мои схемы.

▍ Design For Testability

После производства микросхемы, очень часто требуется проверить микросхему на работоспособность. Для этого в микросхеме все триггеры заменяются на специальные называемые «сканируемые триггеры», которые позволяют выбирать вместо логики, подключенной к входу триггера, выход предыдущего триггера.

Это позволяет выбирать режим “сканирования”, в котором последовательно на все триггеры перемещаются входные данные, затем режим сканирования выключается, и на тактовый сигнал подаётся один такт, затем результаты снова перемещаются, используя цепочку триггеров на выход, и выход сравнивается с эталонным. Если одна из ячеек повреждена, то выходные данные не будут совпадать с эталонными значениями. Входные данные называются Test pattern.

На самом деле я очень упростил всё, и даже не рассказал про Observability, Testability, Stuck-At, At-speed-testing и огромную кучу всего, но нас это не касается, поскольку для sky130 нет готовых инструментов создания паттернов и замены ячеек на сканируемые. У Synopsys есть ПО, которое называется TetraMAX для создания DFT и их паттернов.

UPD: Есть Cloud-V/Fault.

Источник примера.

▍ Floorplan

Floorplan, один из достаточно ручных шагов. На этом этапе, бородатые дяденьки, сидят и анализируют RTL код и Design Constraints для того, чтобы определить идеальное расположение макрокомпонентов. Макрокомпоненты это Mixed/Analog или даже цифровые блоки, которые будут использоваться в вашем конечном компоненте/интегральной схеме.

В маленьких компонентах задержки между компонентами практически не влияют на частоту схему, но в больших компонентах и микросхемах, длительность одного такта становится сравнительной к длительности перемещения сигнала, между компонентами, либо даже имеет длину в несколько тактов. Из-за этого выбор местоположения компонентов может иметь критическое значение на производительность, задержки или даже на энергопотребление.

К сожалению OpenLane, хотя и имеет механизм установки компонентов в конкретных координатах, не обладает теми же инструментами, что Fusion Compiler, ICC II, Innovus и прочие, которые позволяют анализировать связи между макрокомпонентами. OpenLane, может сам выбирать местоположение компонентов, тем не менее этот выбор редко самый оптимальный.

После определения местоположения, также генерируется несколько групп ячейки.

▍ TAP ячейки

Далее в статье мы увидим ошибку о том, что наша стандартная ячейка, не имеет подключения PWELL/NWELL. Эти подключения называются Bulk-ом транзистора. В старых технологиях, подключения BULK были в каждой ячейке, но в новых технологиях длина затвора транзистора была настолько маленькой, что подключения к Bulk, используя контакты начали мешать, поскольку занимали значительную часть в слое контакта, ограничивая уменьшения высоты стандартной ячейки.

Для решения этой проблемы с определённой периодичностью, обычно каждые 30 микрометров, по всей площади вставляются TAP ячейки, который содержат подключения PWELL/NWELL. Каждой TAP ячейки в sky130, хватает, только на 15 микрометров.

Для более развитых технологий, также используются следующие ячейки (необязательно для чтения)

▍ Boundary ячейки

Boundary ячейки используются для того, чтобы разделить макрокомпоненты и места размещения ячейки из стандартной библиотеки. В sky130, судя по всему необходимость в них отсутствует, но в более развитых технологиях, эти ячейки нужны для того, чтобы защитить полисиликоны стандартной ячейки. Если бы Boundary ячейки отсутствовали в этих технологиях во время производства полисиликона по сторонам активного транзистора, то полисиликон транзистора будет разъеден кислотой сильнее, чем соседних транзисторов, вызывая очень неприятные последствия.

▍ Spare ячейки

Иногда после производства микросхемы, бывает необходимость внести изменения в микросхему. Если такая необходимость возникнет, добавление транзисторов является проблемой, поскольку для того, чтобы добавить транзисторы, нужно внести изменения в значительное количество слоёв, например: Полисиликон, N-имплант, P-имплант, Диффузии и другие.

Для решения этой проблемы предварительно расположены по площади всей микросхемы Spare ячейки. Это группы транзисторов, не подключённых ни к чему полезному, но контакты транзистора могут быть подключены для формирования разных ячеек, внося изменения только в металлические слои. В OpenLane эти ячейки не реализованы.

▍ Decap ячейки

Decap используются для того, чтобы загладить влияние высокочастотных компонентов на напряжение питания. Поскольку цифровые микросхемы имеют значительные частоты, и переходы между состояниями вызывают падения напряжения из-за сопротивления линий и огромных токов во время этих переходов.

Во время перехода из одного состояния в другую, цифровые компоненты потребляют наибольший ток и имеют крайне высокие частоты, поэтому влияние цифровых компонентов на напряжение аналоговых компонентов, что для аналоговых компонентов используются отдельные линии подачи питания VDDA/VSSA.

Влияние на друг друга, насколько высоко, что возникает необходимость в Decap ячейках, которые являются ничем иным, чем конденсаторами, который заглаживают изменения в напряжении. Decap конденсаторы заряжаются между переходами, и когда переход начинается, этот конденсатор заглаживает изменения напряжения.

▍ Filler ячейки

Filler ячейки используются для того, чтобы закрыть ячейки для стандартной ячейки, который остались пустыми. Эта необходимость есть, поскольку многие слои не могут содержать прерываний (дырок), поскольку эти прерывания должны иметь размер в минимум 3 ячейки. Если какая-то стандартная ячейка осталась без соседа, то если расстояния между двумя стандартными ячейками получилась, например, в 2 ячейки, то у вас будет ошибка DRC.

Также Filler ячейки необходимы, поскольку пустые места для стандартной ячейки могут не содержать подключения металлов для линий VDD/VSS. В sky130 необходимость отсутствует, но в более продвинутых технологиях, без Filler ячейки не обойтись.

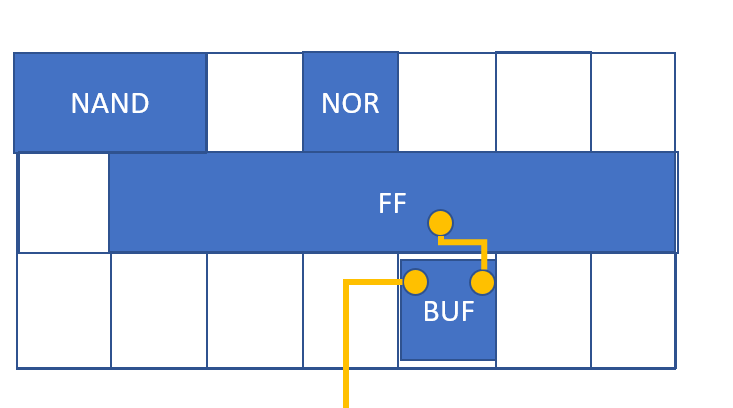

▍ Placement

В этом шаге мы имеем все ячейки, которые должны быть расположены по площади нашего макрокомпонента либо микросхемы, и их потенциальные расположения. Используя эту информацию инструмент Placement-а рассчитывает оптимальное расположение ячейки, и пытается сохранить плотность компонентов не выше, чем параметр Target Utilization. Не буду вдаваться в подробности, вкратце алгоритмы минимизируют задержку от входов макро ячейки, или выходных других ячеек до конкретной ячейки.

К сожалению, я не нашёл способа хорошо продемонстрировать это кроме как на примере этой картинки:

▍ Clock Tree Synthesis

В прошлом шаге мы предполагали, что сигналы тактования синхронных компонентов вроде триггеров, поступают единовременно. В реальности это невозможно, поэтому тактовые сигналы подключаются специальным методом, который вводит дополнительные задержки, чтобы гарантировать, что синхросигнал пребудет к триггеру почти единовременно. Я не буду дальше раскрывать эту тему, хотя она очень интересная и важная.

Рекомендую посмотреть данный плейлист на ютубе, именно на английском, если хотите подробнее узнать о Clock Tree Synthesis.

▍ Routing

После того как мы установили наши стандартные ячейки и подключили синхросигналы, переходим к ещё одному важному этапу, подключениям. На этом шаге инструмент Routing-а подключает все входы и выходы компонентов и ячейки, добавляя буферы и инверторы, для того чтобы компенсировать потери и паразитные ёмкости.

▍ Signoff

На этом шаге результаты приводятся результаты проверки DRC, LVS, которые полностью соответствуют тем же шагам из Custom Design Flow, но дополнительно добавляется шаг Static Timing Analysis, который проверяет время прибытия данных и синхросигналов для того, чтобы удостовериться, что не нарушаются требования триггера, по времени прибытия данных (Setup Timing) и по времени, когда входные данные меняются (Hold Timing). Для этого в OpenLane используется OpenSTA. Хотя это и важные вещи, которые стоит обсудить, я не буду об этом говорить в текущей статье. Для интересующихся, есть упомянутые видосики, либо огромное количество материала везде, начиная от учебников до статей.

Формальное сравнение используется для того, чтобы сравнить исходный RTL код и выходной netlist, который содержит все компоненты в том числе буферы. Несмотря на это, очень редко выходит ошибка сравнения, ибо один из шагов вносил ошибочные изменения из-за бага в инструменте, или из-за ошибки в файлах библиотеки.

▍ Библиотека Стандартной ячейки

Для того чтобы создать какую-либо схему нам нужны компоненты для этой схемы. Эти компоненты содержатся в Библиотеке Стандартной ячейки. Кроме layout файлов, также содержится lef файлы, .lib файлы и SPICE netlist файлы.

Lef файлы содержат лишь слои необходимые для подключения к ячейке или компоненту, этот файл крайне полезен, ибо позволяет не нагружать PnR инструменты лишними слоями, и это может быть крайне важно в случаях, когда количество компонентов превышает миллионы.

Пример LEF файла нашей NAND ячейки:

.lib используется для того, чтобы без симуляции дать необходимую информацию о выходных характеристиках сигнала в зависимости от нагрузочного конденсатора, информацию о характеристиках сигнала входных сигналов, входных конденсаторах, задержках и так далее.

SPICE netlist очень редко используется для симуляций Mixed-Signal компонентов, и изредка для более точной симуляции информации о задержках.

В этой части мы разберём разработку элементарной ячейки на примере элемента NAND.

Требование заказчика к нашей NAND

Требование заказчика, это такой кусок информации, который содержит список требований к характеристикам и функционалу нашего компонента. Вот, давайте разберём на примере:

▍ Нагрузочный конденсатор

Особенность CMOS логики в том, что входы имеют ёмкость, поэтому для того чтобы провести симуляцию нашей модели, нам нужно подключить конденсаторную ёмкость на выходе нашего компонента. Для этого мы взяли 20 фемтоФарад, поскольку именно такая указана ёмкость, которую наш компонент должен поддерживать.

Обычно в библиотеке у нас есть много вариантов одной логической ячейки. Например, у нас могут быть инверторы, которые могут нести 20 фемтоФарад, 40 фемтоФарад и так до, например, 320 фемтоФарад.

Чтобы не указывать конкретное значение, поскольку само значение ничего не значит, без информации о входной ёмкости каждой ячейки, был придуман параметр «размер» ячейки. Все стандартные ячейки используют стандарт де-факто, в котором размером 1 берут ёмкость четырёх инверторов размера 1.

А размер 1 инвертора берётся так, чтобы идеально иметь два транзистора PMOS/NMOS с конкретным размером диффузий. Если вы попробуйте увеличить размер транзистора, то у вас ничего не получится, поскольку ваша стандартная библиотека имеет заранее продуманные размеры NWELL/PWELL и диффузий, в которые просто физически невозможно поместить больше транзисторов.

Вот, например, инвертор 1 и инвертор 4 рядом, как видим, точки соприкосновения идеально совпадают:

▍ Corner cases, напряжение и температура

После производства чипа, транзисторы могут получиться как слабыми, так и более сильными чем типичный случай. Для того, чтобы произвести симуляцию PDK имеет три варианта моделей։ FF, TT и SS, они расшифровываются вот так։ Fast-Fast, Typical-Typical и Slow-Slow. Первый знак определяет характеристики NMOS, а второй PMOS. Бывают и другие вариации.

Также на характеристики транзистора влияет важный параметр температуры. Выше температура — больше сопротивление, транзисторы медленнее и имеют меньший ток в открытом состоянии.

Я не нашёл информацию о поддерживаемых значениях температуры, поэтому возьмём её от балды -40 до +125. Из документации мы узнаём, что модели некоторых ячеек работают между -50 до +150 градусов, но про остальные ячейки информации ноль. Предположим, что все ячейки будут адекватно работать под наши значения от балды.

В свою очередь, напряжение питания, так же влияет на время перехода выхода из одного состояния в другое. Выше напряжение — переход происходит быстрее, ниже напряжение — медленнее. Для этого проекта, мы возьмём центральное значение 1.8В, поскольку используем транзисторы, типичное рабочее напряжение которого 1.8В. Из документации мы увидим, что модели транзисторов, которые мы будем использовать, поддерживают напряжение до 1.95В. Давайте возьмём границу сверху 1.95В (1.8 + 0.15) и соответственно границу снизу 1.65В (1.8-0.15).

Зачем нам это знать? Чтобы измерить максимальную частоту, время Rise/Fall time и задержку нам нужно использовать самый медленный вариант нашей схемы։ SS, минимальное напряжение и высокую температуру. А чтобы измерить потребляемую мощность нужно использовать низкую температуру, высокое напряжение и вариант FF, поскольку быстрые транзисторы потребляют бОльшую мощность. В этой части мы не будем измерять потребляемую мощность.

▍ Rise time и Fall time

Чтобы понять эти два параметра давайте возьмём обычный инвертор и нарисуем графики его выхода. Мы увидим, что изменение из нуля в единицу и обратно происходит не сразу. Дело в том, что на выходе CMOS логики обычно подключена другая CMOS логика, которая имеет ёмкость, которую нужно зарядить, либо разрядить.

Чтобы подсказать инструменту, насколько быстро происходит переход из одного состояния в другое, используются эти два параметра. Rise time измеряется с момента пересечения выходного сигнала 10% от напряжения питания до момента пересечения 90%. Аналогично Fall Time измеряет обратный процесс.

Зелёным отмечен Fall Time и синим Rise time:

▍ Задержка

Кроме времени перехода, также у ячейки, есть очень важная характеристика: Задержка. Задержка описывает время, необходимое, чтобы изменение на входе вызвали изменения на выходе. Для её измерения мы берём момент, когда вход пересекает 50% от напряжения источника и момент, когда выход преодолевает те же 50%. 50% взято неспроста, это нужно для того, чтобы минимизировать влияние Rise/Fall Time. Для максимальной точности измеряются задержки всех комбинаций переходов.

Не буду вдаваться в подробности, если вас интересует: standard cell delay.

Также стоит отметить, что ячейки имеющие состояния, например, триггеры имеют другие временные параметры: Setup Time, Hold Time, Removal Time, Revoery Timer и другие. Я решил их не освещать в этой статье, хотя это очень часто и остается нераскрытой темой.

▍ Площадь компонента

Это важный параметр, поскольку иногда размер подложки имеет критическое значение. Чтобы измерить этот параметр просто берём рулетку, меряем высоту, меряем длину, умножаем.

Например, 2.72мкм на 1.77 мкм = 4.8144 мкм^2.

▍ Как измерять мощность

У наших компонентов два важных параметра мощности. Активная и мощность утечки (Leakage Power). Но важно учесть, что наши компоненты потребляют наибольшую мощность в FF corner, с максимальным напряжением: 1.95В и при минимальной температуре.

Если наша потребляемая мощность соответствует спецификации при данных условиях, то в других состояниях, потребляемая мощность очевидно будет меньше, а значит тем более будет удовлетворять нашим требованиям.

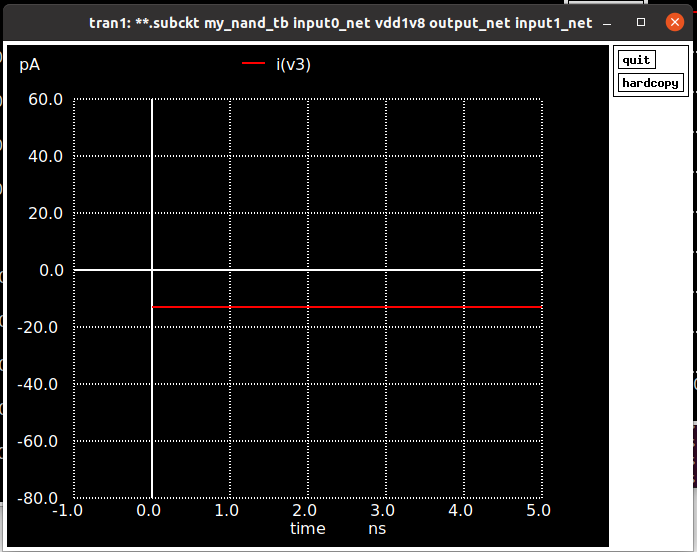

Мощность утечки, эта та мощность, которую наш компонент потребляет в режиме простоя. Для его подсчёта, мы берём наш компонент и измеряем его мощность, с подачей на вход константных значений.

Вот, например график тока. Умножив его на наше напряжение, которое мы взяли 1.95В мы получаем мощность утечки:

Для измерения активной мощности компонента, на вход подают тестовый паттерн, который постоянно повторяется. Затем считают среднее значение мощности по длине всего паттерна.

Очевидно, что вручную никто эти параметры не считает, для этого есть .measure, который может в автоматическом режиме измерять абсолютно все требуемые параметры.

▍ Функция ячейки

Функция ячейки, это информация о том, как эта ячейка будет себя вести при определённых обстоятельствах. Например, при подаче на оба входа NAND сигнала 0, у нас на выходе будет единица. Обычно она даётся в форме таблицы, либо в виде типа ячейки.

Вот наш результат, сравним с таблицей и видим, что они полностью соответствуют друг другу:

Познакомились с теорией, теперь давайте установим необходимые инструменты, а затем приступим к практике в следующих частях.

Об авторе

Меня зовут Арман и я окончил институт Synopsys по профилю VLSI разработки микросхем. В основном я занимаюсь разработкой цифровых компонентов для микросхем и IP для ПЛИС. В прошлом я был программистом, писал бэкенд на Node.js и разрабатывал под микроконтроллеры, но решил пересесть на что-то сложнее, попробовать себя, так сказать.

Я открыт к найму, поэтому, если вас интересует найм разработчика цифровых микросхем с тремя годами опыта и очень интересными проектами (Радио-модемы, преобразователи интерфейсов, процессоры и очень многое) напишите мне в личку.

Как разработать микросхему, от идеи до результата. Ссылки на все статьи։

Как сделать микросхему

Микросхема это электронная схема, которая располагается на пластинке, сделанной из полупроводникового материала, обычно из кремния. Как правило, площадь типичной интегральной схемы составляет 1,5 мм2 , а толщина – 0,2 миллиметра. Все элементы схемы (резисторы, диоды, транзисторы, сопротивления и соединяющие их проводки) размещаются на пластинке.

Вам понадобится

- — паяльник;

- — пластик;

- — провода.

Инструкция

Воспользуйтесь специальным приложением, чтобы продумать конструкцию микросхемы. Попрактиковаться в вопросе инженерии микросхем можно с помощью программы Logisim. Скачать приложение можно по ссылке http://sourceforge.net/projects/circuit/.

Чтобы выполнить конечное проектирование схемы из слоев проводников, диэлектриков и полупроводников, установите приложение Electric VLSI. Скачать его можно на официальном сайте производителя http://www.staticfreesoft.com/productsFree.html. После того, как вам удалось составить электронный проект микросхемы, приступите к ее созданию.

Возьмите кусочек пластика, размер его должен быть как сим-карта телефона. В радиомагазине приобретите токопроводящий карандаш, который предназначен для восстановления дорожек. Возьмите токопроводящий клей, например «Контактол» и шприц.

Для корпуса микросхемы найдите металлическую коробочку. Также найдите небольшое количество тонких проводков для дискретных компонентов.

Приступите к конструированию микросхемы. Нарисуйте на пластинке токопроводящие дорожки, резисторы и емкости, все, что можно нарисовать согласно построенной схемы на компьютере. Далее наклейте транзисторы или диоды. Приклейте на пластинку провода вывода микросхемы. Лучше всего проколоть пластик, чтобы все выводы переместились в низ платы. Сверху приклейте крышку, надпишите на ней название.

Припаяйте полученную микросхему к плате. Для этого приклейте ее выводами на кусочек самоклеющейся алюминиевой фольги, к каждой ноге припаяйте тонкий проводок. Для пайки микросхемы используйте флюс ЛТИ-120. Сделайте плату из стеклотекстолита, разместите на ней схему, сформируйте и припаяйте выходы на площадки платы. Затем возьмите спирт, отмойте плату от остатков флюса. Далее припаяйте навесные элементы.

Видео по теме

Войти на сайт

или

Забыли пароль?

Еще не зарегистрированы?

This site is protected by reCAPTCHA and the Google Privacy Policy and Terms of Service apply.

Как делают микросхемы

Как устроен КМОП-транзистор

Шаг 1. Выращивание болванок

Шаг 2. Нанесение защитной пленки диэлектрика (SiO2)

Шаг 3. Нанесение фоторезистива

Шаг 4. Литография

Шаг 5. Травление

Шаг 6. Диффузия (ионная имплантация)

Шаг 7. Напыление и осаждение

Шаг 8. Заключительный этап

Перспективные технологии

Говоря о процессорах Intel, часто используют такие специфические

понятия, как 0,13-микронный технологический процесс, а в последнее время — 90-нанометровый

технологический процесс. К примеру, принято говорить, что новый процессор Intel

Pentium 4 с ядром Northwood выполнен по 0,13-микронной технологии, а будущее

поколение процессоров будет основано на 90-нанометровом технологическом процессе.

В чем же разница между этими технологическими процессами и как она отражается

на возможностях самих процессоров?

Как делают микросхемы

тобы

понять, в чем заключается основное различие между этими двумя технологиями,

необходимо сделать краткий экскурс в саму технологию производства современных

процессоров или интегральных микросхем.

Как известно из школьного курса физики, в современной электронике основными

компонентами интегральных микросхем являются полупроводники p-типа и n-типа

(в зависимости от типа проводимости). Полупроводник — это вещество, по проводимости

превосходящее диэлектрики, но уступающее металлам. Основой полупроводников обоих

типов может служить кремний (Si), который в чистом виде (так называемый собственный

полупроводник) плохо проводит электрический ток, однако добавление (внедрение)

в кремний определенной примеси позволяет радикально изменить его проводящие

свойства. Существует два типа примеси: донорная и акцепторная. Донорная примесь

приводит к образованию полупроводников n-типа c электронным типом проводимости,

а акцепторная — к образованию полупроводников p-типа с дырочным типом проводимости.

Контакты p- и n-полупроводников позволяют формировать транзисторы — основные

структурные элементы современных микросхем. Такие транзисторы, называемые КМОП-транзисторами,

могут находиться в двух основных состояниях: открытом, когда они проводят электрический

ток, и запертом — при этом они электрический ток не проводят. Поскольку КМОП-транзисторы

являются основными элементами современных микросхем, поговорим о них подробнее.

Как устроен КМОП-транзистор

Простейший КМОП-транзистор n-типа имеет три электрода: исток, затвор и сток.

Сам транзистор выполнен в полупроводнике p-типа с дырочной проводимостью, а

в областях стока и истока формируются полупроводники n-типов с электронной проводимостью.

Естественно, что за счет диффузии дырок из p-области в n-область и обратной

диффузии электронов из n-области в p-область на границах переходов p- и n-областей

формируются обедненные слои (слои, в которых отсутствуют основные носители зарядов).

В обычном состоянии, то есть когда к затвору не прикладывается напряжение, транзистор

находится в «запертом» состоянии, то есть не способен проводить ток от истока

к стоку. Ситуация не меняется, даже если приложить напряжение между стоком и

истоком (при этом мы не принимаем во внимание токи утечки, вызванные движением

под воздействием формируемых электрических полей неосновных носителей заряда,

то есть дырок для n-области и электронов для p-области).

Однако если к затвору приложить положительный потенциал (рис.

1), то ситуация в корне изменится. Под воздействием электрического поля

затвора дырки выталкиваются в глубь p-полупроводника, а электроны, наоборот,

втягиваются в область под затвором, образуя обогащенный электронами канал между

истоком и стоком. Если приложить к затвору положительное напряжение, эти электроны

начинают двигаться от истока к стоку. При этом транзистор проводит ток — говорят,

что транзистор «открывается». Если напряжение с затвора снимается, электроны

перестают втягиваться в область между истоком и стоком, проводящий канал разрушается

и транзистор перестает пропускать ток, то есть «запирается». Таким образом,

меняя напряжение на затворе, можно открывать или запирать транзистор, аналогично

тому, как можно включать или выключать обычный тумблер, управляя прохождением

тока по цепи. Именно поэтому транзисторы иногда называют электронными переключателями.

Однако, в отличие от обычных механических переключателей, КМОП-транзисторы практически

безынерционны и способны переходить из открытого в запертое состояние триллионы

раз в секунду! Именно этой характеристикой, то есть способностью мгновенного

переключения, и определяется в конечном счете быстродействие процессора, который

состоит из десятков миллионов таких простейших транзисторов.

Итак, современная интегральная микросхема состоит из десятков миллионов простейших

КМОП-транзисторов. Остановимся более подробно на процессе изготовления микросхем,

первый этап которого — получение кремниевых подложек.

Шаг 1. Выращивание болванок

Создание таких подложек начинается с выращивания цилиндрического по форме монокристалла

кремния. В дальнейшем из таких монокристаллических заготовок (болванок) нарезают

круглые пластины (wafers), толщина которых составляет приблизительно 1/40 дюйма,

а диаметр — 200 мм (8 дюймов) или 300 мм (12 дюймов). Это и есть кремниевые

подложки, служащие для производства микросхем.

При формировании пластин из монокристаллов кремния учитывается то обстоятельство,

что для идеальных кристаллических структур физические свойства в значительной

степени зависят от выбранного направления (свойство анизотропии). К примеру,

сопротивление кремниевой подложки будет различным в продольном и поперечном

направлениях. Аналогично, в зависимости от ориентации кристаллической решетки,

кристалл кремния будет по-разному реагировать на какие-либо внешние воздействия,

связанные с его дальнейшей обработкой (например, травление, напыление и т.д.).

Поэтому пластина должна быть вырезана из монокристалла таким образом, чтобы

ориентация кристаллической решетки относительно поверхности была строго выдержана

в определенном направлении.

Как уже отмечалось, диаметр заготовки монокристалла кремния составляет либо

200, либо 300 мм. Причем диаметр 300 мм — это относительно новая технология,

о которой мы расскажем ниже. Понятно, что на пластине такого диаметра может

разместиться далеко не одна микросхема, даже если речь идет о процессоре Intel

Pentium 4. Действительно, на одной подобной пластине-подложке формируется несколько

десятков микросхем (процессоров), но для простоты мы рассмотрим лишь процессы,

происходящие на небольшом участке одного будущего микропроцессора.

Шаг 2. Нанесение защитной пленки диэлектрика (SiO2)

После формирования кремниевой подложки наступает этап создания сложнейшей полупроводниковой

структуры.

Для этого в кремний нужно внедрить так называемые донорную и акцепторную примеси.

Однако возникает вопрос — как осуществить внедрение примесей по точно заданному

рисунку-шаблону? Для того чтобы это стало возможным, те области, куда не требуется

внедрять примеси, защищают специальной пленкой из диоксида кремния, оставляя

оголенными только те участки, которые подвергаются дальнейшей обработке (рис.

2). Процесс формирования такой защитной пленки нужного рисунка состоит из

нескольких этапов.

На первом этапе вся пластина кремния целиком покрывается тонкой пленкой диоксида

кремния (SiO2), который является очень хорошим изолятором и выполняет функцию

защитной пленки при дальнейшей обработке кристалла кремния. Пластины помещают

в камеру, где при высокой температуре (от 900 до 1100 °С) и давлении происходит

диффузия кислорода в поверхностные слои пластины, приводящая к окислению кремния

и к образованию поверхностной пленки диоксида кремния. Для того чтобы пленка

диоксида кремния имела точно заданную толщину и не содержала дефектов, необходимо

строго поддерживать постоянную температуру во всех точках пластины в процессе

окисления. Если же пленкой из диоксида кремния должна быть покрыта не вся пластина,

то предварительно на кремниевую подложку наносится маска Si3N4, предотвращающая

нежелательное окисление.

Шаг 3. Нанесение фоторезистива

После того как кремниевая подложка покроется защитной пленкой диоксида кремния,

необходимо удалить эту пленку с тех мест, которые будут подвергаться дальнейшей

обработке. Удаление пленки осуществляется посредством травления, а для защиты

остальных областей от травления на поверхность пластины наносится слой так называемого

фоторезиста. Термином «фоторезисты» обозначают светочувствительные и устойчивые

к воздействию агрессивных факторов составы. Применяемые составы должны обладать,

с одной стороны, определенными фотографическими свойствами (под воздействием

ультрафиолетового света становиться растворимыми и вымываться в процессе травления),

а с другой — резистивными, позволяющими выдерживать травление в кислотах и щелочах,

нагрев и т.д. Основное назначение фоторезистов — создание защитного рельефа

нужной конфигурации.

Процесс нанесения фоторезиста и его дальнейшее облучение ультрафиолетом по заданному

рисунку называется фотолитографией и включает следующие основные операции: формирование

слоя фоторезиста (обработка подложки, нанесение, сушка), формирование защитного

рельефа (экспонирование, проявление, сушка) и передача изображения на подложку

(травление, напыление и т.д.).

Перед нанесением слоя фоторезиста (рис. 3) на подложку

последняя подвергается предварительной обработке, в результате чего улучшается

ее сцепление со слоем фоторезиста. Для нанесения равномерного слоя фоторезиста

используется метод центрифугирования. Подложка помещается на вращающийся диск

(центрифуга), и под воздействием центробежных сил фоторезист распределяется

по поверхности подложки практически равномерным слоем. (Говоря о практически

равномерном слое, учитывают то обстоятельство, что под действием центробежных

сил толщина образующейся пленки увеличивается от центра к краям, однако такой

способ нанесения фоторезиста позволяет выдержать колебания толщины слоя в пределах

±10%.)

Шаг 4. Литография

После нанесения и сушки слоя фоторезиста наступает этап формирования необходимого

защитного рельефа. Рельеф образуется в результате того, что под действием ультрафиолетового

излучения, попадающего на определенные участки слоя фоторезиста, последний изменяет

свойства растворимости, например освещенные участки перестают растворяться в

растворителе, которые удаляют участки слоя, не подвергшиеся освещению, или наоборот

— освещенные участки растворяются. По способу образования рельефа фоторезисты

делят на негативные и позитивные. Негативные фоторезисты под действием ультрафиолетового

излучения образуют защитные участки рельефа. Позитивные фоторезисты, напротив,

под воздействием ультрафиолетового излучения приобретают свойства текучести

и вымываются растворителем. Соответственно защитный слой образуется в тех участках,

которые не подвергаются ультрафиолетовому облучению.

Для засветки нужных участков слоя фоторезиста используется специальный шаблон-маска.

Чаще всего для этой цели применяются пластинки из оптического стекла с полученными

фотографическим или иным способом непрозрачными элементами. Фактически такой

шаблон содержит рисунок одного из слоев будущей микросхемы (всего таких слоев

может насчитываться несколько сотен). Поскольку этот шаблон является эталоном,

он должен быть выполнен с большой точностью. К тому же с учетом того, что по

одному фотошаблону будет сделано очень много фотопластин, он должен быть прочным

и устойчивым к повреждениям. Отсюда понятно, что фотошаблон — весьма дорогая

вещь: в зависимости от сложности микросхемы он может стоить десятки тысяч долларов.

Ультрафиолетовое излучение, проходя сквозь такой шаблон (рис.

4), засвечивает только нужные участки поверхности слоя фоторезиста. После

облучения фоторезист подвергается проявлению, в результате которого удаляются

ненужные участки слоя. При этом открывается соответствующая часть слоя диоксида

кремния.

Несмотря на кажущуюся простоту фотолитографического процесса, именно этот этап

производства микросхем является наиболее сложным. Дело в том, что в соответствии

с предсказанием Мура количество транзисторов на одной микросхеме возрастает

экспоненциально (удваивается каждые два года). Подобное возрастание числа транзисторов

возможно только благодаря уменьшению их размеров, но именно уменьшение и «упирается»

в процесс литографии. Для того чтобы сделать транзисторы меньше, необходимо

уменьшить геометрические размеры линий, наносимых на слой фоторезиста. Но всему

есть предел — сфокусировать лазерный луч в точку оказывается не так-то просто.

Дело в том, что в соответствии с законами волновой оптики минимальный размер

пятна, в который фокусируется лазерный луч (на самом деле это не просто пятно,

а дифракционная картина), определяется кроме прочих факторов и длиной световой

волны. Развитие литографической технологии со времени ее изобретения в начале

70-х шло в направлении сокращения длины световой волны. Именно это позволяло

уменьшать размеры элементов интегральной схемы. С середины 80-х в фотолитографии

стало использоваться ультрафиолетовое излучение, получаемое с помощью лазера.

Идея проста: длина волны ультрафиолетового излучения меньше, чем длина волны

света видимого диапазона, следовательно, возможно получить и более тонкие линии

на поверхности фоторезиста. До недавнего времени для литографии использовалось

глубокое ультрафиолетовое излучение (Deep Ultra Violet, DUV) с длиной волны

248 нм. Однако когда фотолитография перешагнула границу 200 нм, возникли серьезные

проблемы, впервые поставившие под сомнение возможность дальнейшего использования

этой технологии. Например, при длине волны меньше 200 мкм слишком много света

поглощается светочувствительным слоем, поэтому усложняется и замедляется процесс

передачи шаблона схемы на процессор. Подобные проблемы побуждают исследователей

и производителей искать альтернативу традиционной литографической технологии.

Новая технология литографии, получившая название ЕUV-литографии (Extreme UltraViolet

— сверхжесткое ультрафиолетовое излучение), основана на использовании ультрафиолетового

излучения с длиной волны 13 нм.

Переход с DUV- на EUV-литографию обеспечивает более чем 10-кратное уменьшение

длины волны и переход в диапазон, где она сопоставима с размерами всего нескольких

десятков атомов.

Применяемая сейчас литографическая технология позволяет наносить шаблон с минимальной

шириной проводников 100 нм, в то время как EUV-литография делает возможной печать

линий гораздо меньшей ширины — до 30 нм. Управлять ультракоротким излучением

не так просто, как кажется. Поскольку EUV-излучение хорошо поглощается стеклом,

то новая технология предполагает использование серии из четырех специальных

выпуклых зеркал, которые уменьшают и фокусируют изображение, полученное после

применения маски (рис. 5, 6, 7).

Каждое такое зеркало содержит 80 отдельных металлических слоев толщиной примерно

в 12 атомов.

Шаг 5. Травление

После засвечивания слоя фоторезиста наступает этап травления (etching) с целью

удаления пленки диоксида кремния (рис. 8).

Часто процесс травления ассоциируется с кислотными ваннами. Такой способ травления

в кислоте хорошо знаком радиолюбителям, которые самостоятельно делали печатные

платы. Для этого на фольгированный текстолит лаком, выполняющим функцию защитного

слоя, наносят рисунок дорожек будущей платы, а затем опускают пластину в ванну

с азотной кислотой. Ненужные участки фольги стравливаются, обнажая чистый текстолит.

Этот способ имеет ряд недостатков, главный из которых — невозможность точно

контролировать процесс удаления слоя, так как слишком много факторов влияют

на процесс травления: концентрация кислоты, температура, конвекция и т.д. Кроме

того, кислота взаимодействует с материалом по всем направлениям и постепенно

проникает под край маски из фоторезиста, то есть разрушает сбоку прикрытые фоторезистом

слои. Поэтому при производстве процессоров используется сухой метод травления,

называемый также плазменным. Такой метод позволяет точно контролировать процесс

травления, а разрушение вытравливаемого слоя происходит строго в вертикальном

направлении.

При использовании сухого травления для удаления с поверхности пластины диоксида

кремния применяется ионизированный газ (плазма), который вступает в реакцию

с поверхностью диоксида кремния, в результате чего образуются летучие побочные

продукты.

После процедуры травления, то есть когда оголены нужные области чистого кремния,

удаляется оставшаяся часть фотослоя. Таким образом, на кремниевой подложке остается

рисунок, выполненный диоксидом кремния.

Шаг 6. Диффузия (ионная имплантация)

Напомним, что предыдущий процесс формирования необходимого рисунка на кремниевой

подложке требовался для того, чтобы создать в нужных местах полупроводниковые

структуры путем внедрения донорной или акцепторной примеси. Процесс внедрения

примесей осуществляется посредством диффузии (рис. 9) —

равномерного внедрения атомов примеси в кристаллическую решетку кремния. Для

получения полупроводника n-типа обычно используют сурьму, мышьяк или фосфор.

Для получения полупроводника p-типа в качестве примеси используют бор, галлий

или алюминий.

Для процесса диффузии легирующей примеси применяется ионная имплантация. Процесс

имплантации заключается в том, что ионы нужной примеси «выстреливаются» из высоковольтного

ускорителя и, обладая достаточной энергией, проникают в поверхностные слои кремния.

Итак, по окончании этапа ионной имплантации необходимый слой полупроводниковой

структуры создан. Однако в микропроцессорах таких слоев может насчитываться

несколько. Для создания очередного слоя на полученном рисунке схемы выращивается

дополнительный тонкий слой диоксида кремния. После этого наносятся слой поликристаллического

кремния и еще один слой фоторезиста. Ультрафиолетовое излучение пропускается

сквозь вторую маску и высвечивает соответствующий рисунок на фотослое. Затем

опять следуют этапы растворения фотослоя, травления и ионной имплантации.

Шаг 7. Напыление и осаждение

Наложение новых слоев осуществляется несколько раз, при этом для межслойных

соединений в слоях оставляются «окна», которые заполняются атомами металла;

в результате на кристалле создаются металлические полоски — проводящие области.

Таким образом в современных процессорах устанавливаются связи между слоями,

формирующими сложную трехмерную схему. Процесс выращивания и обработки всех

слоев длится несколько недель, а сам производственный цикл состоит из более

чем 300 стадий. В результате на кремниевой пластине формируются сотни идентичных

процессоров.

Чтобы выдержать воздействия, которым подвергаются пластины в процессе нанесения

слоев, кремниевые подложки изначально делаются достаточно толстыми. Поэтому,

прежде чем разрезать пластину на отдельные процессоры, ее толщину уменьшают

на 33% и удаляют загрязнения с обратной стороны. Затем на тыльную сторону подложки

наносят слой специального материала, улучшающего крепление кристалла к корпусу

будущего процессора.

Шаг 8. Заключительный этап

По окончании цикла формирования все процессоры тщательно тестируются. Затем

из пластины-подложки с помощью специального устройства вырезаются конкретные,

уже прошедшие проверку кристаллы (рис. 10).

Каждый микропроцессор встраивается в защитный корпус, который также обеспечивает

электрическое соединение кристалла микропроцессора с внешними устройствами.

Тип корпуса зависит от типа и предполагаемого применения микропроцессора.

После запечатывания в корпус каждый микропроцессор повторно тестируется. Неисправные

процессоры отбраковывают, а исправные подвергают нагрузочным испытаниям. Затем

процессоры сортируют в зависимости от их поведения при различных тактовых частотах

и напряжениях питания.

Перспективные технологии

Технологический процесс производства микросхем (в частности, процессоров) рассмотрен

нами весьма упрощенно. Но даже такое поверхностное изложение позволяет понять

технологические трудности, с которыми приходится сталкиваться при уменьшении

размеров транзисторов.

Однако, прежде чем рассматривать новые перспективные технологии, ответим на

поставленный в самом начале статьи вопрос: что же такое проектная норма технологического

процесса и чем, собственно, отличается проектная норма 130 нм от нормы 180 нм?

130 нм или 180 нм — это характерное минимальное расстояние между двумя соседними

элементами в одном слое микросхемы, то есть своеобразный шаг сетки, к которой

осуществляется привязка элементов микросхемы. При этом совершенно очевидно,

что, чем меньше этот характерный размер, тем больше транзисторов можно разместить

на одной и той же площади микросхемы.

В настоящее время в производстве процессоров Intel используется 0,13-микронный

технологический процесс. По этой технологии изготавливают процессор Intel Pentium

4 с ядром Northwood, процессор Intel Pentium III с ядром Tualatin и процессор

Intel Celeron. В случае применения такого технологического процесса полезная

ширина канала транзистора составляет 60 нм, а толщина оксидного слоя затвора

не превышает 1,5 нм. Всего же в процессоре Intel Pentium 4 размещается 55 млн.

транзисторов.

Наряду с увеличением плотности размещения транзисторов в кристалле процессора,

0,13-микронная технология, пришедшая на смену 0,18-микронной, имеет и другие

нововведения. Во-первых, здесь используются медные соединения между отдельными

транзисторами (в 0,18-микронной технологии соединения были алюминиевыми). Во-вторых,

0,13-микронная технология обеспечивает более низкое энергопотребление. Для мобильной

техники, например, это означает, что энергопотребление микропроцессоров становится

меньше, а время работы от аккумуляторной батареи — больше.

Ну и последнее нововведение, которое было воплощено при переходе на 0,13-микронный

технологический процесс — это использование кремниевых пластин (wafer) диаметром

300 мм. Напомним, что до этого большинство процессоров и микросхем изготовлялись

на основе 200-миллиметровых пластин.

Увеличение диаметра пластин позволяет снизить себестоимость каждого процессора

и увеличить выход продукции надлежащего качества. Действительно, площадь пластины

диаметром 300 мм в 2,25 раза больше площади пластины диаметром 200 мм, соответственно

и количество процессоров, получаемых из одной пластины диаметром 300 мм, в два

с лишним раза больше.

В 2003 году ожидается внедрение нового технологического процесса с еще меньшей

проектной нормой, а именно 90-нанометрового. Новый технологический процесс,

по которому корпорация Intel будет производить большую часть своей продукции,

в том числе процессоры, наборы микросхем и коммуникационное оборудование, был

разработан на опытном заводе D1C корпорации Intel по обработке 300-миллиметровых

пластин в г.Хиллсборо (шт.Орегон).

23 октября 2002 года корпорация Intel объявила об открытии нового производства

стоимостью 2 млрд. долл. в Рио-Ранчо (шт.Нью-Мексико). На новом заводе, получившем

название F11X, будет применяться современная технология, по которой будут производиться

процессоры на 300-мм подложках с использованием технологического процесса с

проектной нормой 0,13 микрон. В 2003 году завод будет переведен на технологический

процесс с проектной нормой 90 нм.

Кроме того, корпорация Intel уже заявила о возобновлении строительства еще одного

производственного объекта на Fab 24 в Лейкслипе (Ирландия), который предназначен

для изготовления полупроводниковых компонентов на 300-миллиметровых кремниевых

подложках с 90-нанометровой проектной нормой. Новое предприятие общей площадью

более 1 млн. кв. футов с особо чистыми помещениями площадью 160 тыс. кв. футов

предполагается ввести в строй в первой половине 2004 года, и на нем будет работать

более тысячи сотрудников. Стоимость объекта составляет около 2 млрд. долл.

В 90-нанометровом процессе применяется целый ряд передовых технологий. Это

и самые маленькие в мире серийно изготавливаемые КМОП-транзисторы с длиной затвора

50 нм (рис. 11), что обеспечивает рост производительности

при одновременном снижении энергопотребления, и самый тонкий оксидный слой затвора

среди всех когда-либо производившихся транзисторов — всего 1,2 нм (рис.

12), или менее 5 атомарных слоев, и первая в отрасли реализация высокоэффективной

технологии напряженного кремния.

Из перечисленных характеристик в комментариях нуждается, пожалуй, лишь понятие

«напряженного кремния» (рис. 13). В таком кремнии расстояние

между атомами больше, чем в обычном полупроводнике. Это, в свою очередь, обеспечивает

более свободное протекание тока, аналогично тому, как на дороге с более широкими

полосами движения свободнее и быстрее движется транспорт.

В результате всех нововведений на 10-20% улучшаются рабочие характеристики транзисторов,

при увеличении затрат на производство всего на 2%.

Кроме того, в 90-нанометровом технологическом процессе используется семь слоев

в микросхеме (рис. 14), что на один слой больше, чем в

130-нанометровом технологическом процессе, а также медные соединения.

Все эти особенности в сочетании с 300-миллиметровыми кремниевыми подложками

обеспечивают корпорации Intel выигрыш в производительности, объемах производства

и себестоимости. В выигрыше оказываются и потребители, поскольку новый технологический

процесс Intel позволяет продолжить развитие отрасли в соответствии с законом

Мура, вновь и вновь повышая производительность процессоров.

КомпьютерПресс 1’2003

Александр Эрлих

В студии Zelenograd.ru Сергей Ранчин – начальник кристального производства завода «Микрон».

Мы поговорим сегодня о кристальном производстве – сердце микроэлектронного производства. Можно так сказать?

Да, потому что все полупроводниковое производство именно там, где рождаются сами чипы с интегральной схемой, начиная от исходной пластины и до пластины с кристаллами. Все дальнейшие манипуляции – это уже выход изготовленного кристалла до своей конечной цели.

А почему производство «кристальное»? Мы знаем, что такое кристаллы в природе, а что такое кристаллы в микроэлектронике?

Первое, научное объяснение – пластина монокристаллическая. Это часть большого кристалла, порезанная на части. Она имеет определенную кристаллическую структуру, и на этой монокристаллической пластине мы формируем интегральные схемы. И все манипуляции, соответственно, мы совершаем с кусочком кристалла. Ну, а традиционно американское название «чип» — оно ближе к слову «кристалл» — кристальное производство подразумевает под собой это. То есть, «чип» и «кристалл» это идентичные названия. Фактически, я начальник производства чипов. Если брать английскую аббревиатуру — director of chip production.

Естественно, ваше кристальное производство — часть большой технологической цепочки. Что поступает к вам «на вход»? C точки зрения материалов, каких-то технических заданий? Какие именно чипы делать? Что это такое?

Мы обеспечиваем один из самых важных процессов в формировании интегральной схемы, но далеко не единственный. Начало – это целая промышленность – производство исходных материалов. Если брать непосредственно историю Зеленограда, то раньше был завод «Элма», который занимался выращиванием исходного поликремния. А поликремний получается из обычного кварцевого песка, то есть практически мы работаем с исходным материалом, с песком. Из песка получается поликремний, из поликремния уже пластины, которые нарезаются и поступают к нам в производство.

То есть, к вам уже поступает нарезанная пластина?

Да, это исходная пластина, отполированная, с минимальным, считанным количеством дефектов (идеального, безусловно, ничего нет). Дальше все манипуляции с пластиной – это уже непосредственно мое производство.

Помимо пластин, есть некое дизайнерское решение: что это будет за чип, какие действия он будет выполнять?

Изначально в основе всего лежит технология. Это формирование в объеме активных и пассивных элементов, на основании которых, создавая электрические схемы с определенными параметрами, можно делать какие-то конечные устройства. В начале нашего процесса на соответствующей монокристаллической пластине по определенным правилам, так называемой «технологии», с использованием определенного оборудования и определенных операций, формируются активные и пассивные элементы, которые потом соединяются в электрическую схему.

По сути дела, ваша задача – сформировать электрическую схему на пластине?

Моя задача создавать условия и четко, жестко выдерживать параметры в процессе этого производства. Потому что формально, меняя только комплект шаблонов и рисунок, мне все равно, что выпускать: сложные изделия, карточку для метрополитена или сим-карту, карту памяти и т.д. Последовательность операций ровно такая же для всех, меняется только комплект шаблонов, рисунок.

Можно сказать, что это чертеж электрической схемы?

Дизайн.

То есть, грубо говоря, если я открою сейчас какой-нибудь старый телевизор, то там будет большая плата с кучей элементов. Вы, фактически, делаете то же самое, только в маленьком кристалле? Я помню, к старым электронным устройствам прилагались огромные «простыни» со чертежами электрических схем. Такой чертеж поступает к вам «на вход», в некоем компьютеризированном виде?

Совершенно верно, процесс дизайна именно такой. Из пассивных элементов, или из блоков, мини-плат или уже готовых мини-устройств, триггеров, счетных устройств, процессоров компонуется электрическая схема, точно такая же, как на чертеже дизайна. После этого по определенным описанным правилам проектирования, я как изготовитель, гарантирую, что все запланированное на бумаге, я выведу в конечном продукте.

То есть, вы эти правила проектирования передаете сначала дизайнерам, и они уже работают с этими правилами, зная что их задумки, возможно где-то безумные, все равно будут реализованы вашим производством.

На основании базовых элементов. Располагается все от простых элементов – к сложным. Простые элементы – это транзисторы, резисторы, конденсаторы – какие-то пассивные элементы, емкости тоже, в интегральном исполнении. Специальный отдел снимает с них так называемые «спайс-параметры», и дальше преобразует их в те самые правила, по которым собираются эти электрические схемы. Дизайнеры берут эти правила, и на основании них могут формировать так называемые «design kit»: это уже блочные элементы, например – интерфейсную плату, память, какие-то генераторы, блоки взаимодействия, коммутации. Следующий этап – создать из этих блоков определенную схему.

Некую реально работающую схему…

Да. И действительно, зачастую люди далекие от микроэлектроники спрашивают: «Что такое микроэлектроника, «минимальный размер», ну, какая разница: 0.18 микрон – 90 нанометров? Что это такое?». Действительно, все видят платы, зелененькие-синенькие в сотовых телефонах или компьютерах — как правило, люди больше с ними общаются… Телевизоры редко кто разбирает, а телефон у многих падал и разбивался – проще объяснить. На этой плате много различных элементов. Чем выше уровень технологии – тем меньше размер, тем в меньшем размере все эти элементы можно реализовать. Чем «круче» технология – тем меньше размер, тем более миниатюрное устройство с большим функционалом на той же самой единице площади можно сделать. Таким образом определяется и эффективность – пластина одна, а можно сделать одного и того же устройства на этой пластине по разным технологиям разное количество.

То есть чип сам по себе будет дешевле?

Конечно. Дешевле и конечное устройство. Но можно и по-другому подойти – он будет стоить столько же, а работать будет в четыре раза быстрее.

Или меньше энергии потреблять…

Да. Или больше функционала нести в себе.

Насколько я понимаю, так же «на вход» поступают всевозможные химические реактивы.

Не только химические, зачастую и различные материалы – «мишени»…

Ну, всевозможные расходные материалы.

Да, причем требования к ним достаточно чистые, специальные, которые образуют целое производство. Почему говорят, что микроэлектроника – это такое направление, которое за собой тянет несколько других. Раньше это называлось «градообразующее», сейчас говорят «которое за собой тянет развитие в других областях».

Говорят, что одно рабочее место в микроэлектронике создает десять в других областях.

Примерно так, да. Потому что для обеспечения этого выпуска нужно притягивать и химическую промышленность и производство, естественно это производство зависит от уровня технологического оборудования, машиностроения.

Пластины перед тем как запустить в производство, насколько я понимаю, вы загружаете в эти специальные оранжевые SMIF-контейнеры и дальше они уже оттуда людьми не достаются?

Мы их не просто загружаем, мы их еще и однозначно идентифицируем специальной лазерной маркировкой. Например, в чем уникальность билетов – в том, что всегда можно проследить его историю, потому что на каждом этапе мы фактически подписываем каждый чип. Есть разные принципы построение «чистой комнаты». Наша «чистая комната» под проект 180-90 нанометров использует так называемую «SMIF-технологию». В основном, чтобы сэкономить на инфраструктуре, на обеспечении чистоты, потому что любая пылинка несет в себе поражающий фактор и, попадая на пластину, выводит из строя ваше функциональное устройство. И если оно у вас очень сложное, то цена вопроса намного больше. Если у устройства много чипов на пластине, то попадание одной пылинки на один из восьмидесяти тысяч кристаллов, наверное, не так страшно. А если их всего сто, то цена вопроса – один процент минимум.

В этом СМИФ-контейнере маленькая «особо чистая комната»?

Да, она особо чистая. Есть так называемые «классы чистоты». Там создан класс чистоты фактически 0.00-сколько-то там единиц, естественно, в пересчете на кубический метр. Это допустимо – идеального ничего нет, к сожалению. Таким образом, мы, во-первых, экономим, во-вторых – это дополнительная защита от загрязнений, повышение процента выхода годных пластин.

Что происходит с пластиной, когда она уже загружена в SMIF-контейнер?

Много чего происходит. Все операции делаются последовательно, нельзя никакую операцию пропустить, иначе на выходе мы ничего годного не получим. Если брать по-крупному, таких операций около трехсот, а если детализировать каждую операцию, каждую манипуляцию с пластинами, это либо перемещение, либо нанесение какого-то одного из слоев, потому что есть композитные материалы, где несколько раз обрабатывается пластина, то таких операций свыше трех тысяч. Все они делаются последовательно, и если у вас есть какая-то накопленная ошибка, то она дальше действует как усилитель.

Три тысячи разных типов операций или три тысячи операций, которые делаются с пластиной?

Три тысячи операций, которые делают с этой пластиной, чтобы на выходе получить годное изделие – чип, готовый к корпусированию.

А сколько разных именно типов операций?

Они сгруппированы, на каждую операцию выписан отдельный рецепт на установку, который забит и отрабатывается уже не на рабочих пластинах, а зачастую на спутниках. Потому что цена отработки на рабочих пластинах, конечно, очень велика. Например, на 2999-й отрабатывать пластину, на которой сделал столько операций, наверное, бессмысленно. Смысл есть, но очень дорого. Поэтому все это отрабатывается на спутниках, на специальных пластинах. И у нас, более того, это подтверждается каждый раз, то есть мало того, что процесс один раз разработан, он еще должен воспроизводиться изо дня в день, из месяца в месяц, из года в год. Таким образом, мы подтверждаем качество всех этих процессов. Все процессы мы сгруппировали на восемь основных направлений. От восьми до одиннадцати, с разной степенью детализации: процессы фотолитографии, плазмо-химического травления, жидкостной химии и травления… ну, диффузии сейчас уже нет как таковой, но мы уже традиционно называем высокотемпературную обработку диффузией, и, соответственно, высокотемпературными отжигами. CVD – это английская аббревиатура – осаждение диэлектрических или металлических пленок из газовой фазы. PVD – это напыление на пластины металлов, различных проводящих металлических пленок. Далее, безусловно, метрология, потому что с определенной периодичностью на маршруте мы должны контролировать, подтвердить, что все предыдущие операции сделаны качественно. Должны подтвердить непосредственно качество каких-то критических процессов – это либо толщина диэлектрика, осажденного или окисленного, или померить размеры фотолитографии, совпадают они или нет. И два последних процесса – это ионная имплантация и химико-механическая полировка. Если брать по-крупному, то формально это все процессы, которые сейчас у нас есть. На 90 нанометров, которые будут у нас реализованы, будет еще медная металлизация, там будет дополнительное оборудование, это электро-химическое осаждение меди из жидких реагентов.

В чем заключается основной принцип, благодаря которому вы делаете трехмерную структуру на кремниевой пластине?

Принцип в том, что на пластину наносится рисунок, на фотолитографии, дальше с этим рисунком делаются различные манипуляции. Каждый слой несет в себе определенный функционал. Либо делается активная область, либо рисунок активных элементов, проводников, или — есть такое понятие – обкладки конденсаторов, затворы транзисторов, переходные или контактирующие окна между двумя слоями, соединяющие два слоя, например, разводки, или активной структуры. То есть элементы создаются и в объеме пластины и на ее поверхности. Примерно, вся структура составляет до шести микрон в глубину пластины и примерно столько же – шесть микрон и даже больше, в зависимости от функционала и сложности, на поверхности.

Я правильно понимаю, что фотолитография заключается в том, что вы какие-то участки закрываете, грубо говоря, а то, что осталось протравливаете?

Да, там разные есть элементы, но принцип примерно такой. Почему это называется фотолитография: на пластину наносится фоточувствительная пленка, специальный фоторезист, нужна определенная равномерность ее нанесения, с ней необходимо провести определенные модификации, дальше шаблоном формируется рисунок. Позитив-негатив – все точно так же, как в обычной фотографии. И в зависимости от того, какой тип фотолитографии, шаблона и фоторезиста, формируется либо негативный рисунок, либо позитивный. После этого все отправляется в проявитель – все как в фотографии – засвеченные или, наоборот, защищенные места, растворяются в этом проявителе. Таким образом, формируется фоторезист. Он обладает интересными свойстами: он достаточно устойчив к плазме, и несет в себе вязки для проникновения, например, ионной имплантации атомов, которые там полегируются. А после этого идет модификация, как я сказал, либо это травление по этой маске, то есть все слои, которые внизу, плазмой будут потравлены либо до определенного слоя, либо на определенную глубину. Соответственно, так же с фоторезистивной маской, пластины могут пойти в ионную имплантацию. Ионная имплантация – это когда считанное количество атомов определенного вещества разгоняется (чистого — у нас там сепаратор стоит) до определенной энергии и проникает в поверхность на определенную глубину, из-за того, что она обладает энергией, набирает скорость. Она упирается, бьется в пластину и проникает на определенную глубину. Таким образом, достаточно точно можно регулировать количество атомов, примесей и глубину их проникновения.

То есть вы меняете химические свойства вещества в строго определенном месте?

Не химические свойства, а свойства непосредственно самого атома.

Да, само вещество меняется.

Да, само вещество из газовой фазы разгоняется. Если старую физику вспомнить, сейчас уже, наверное, не так это актуально, а когда мы учились, старые телевизоры, электронно-лучевая трубка, поток электронов: две пластины, приложением различного напряжения можно разогнать их до разной скорости, соответственно, если приложить пластины по пучку, то разная масса отклонится на разный уровень. Таким образом, можно очистить весь пучок от других примесей и выделить, посчитать примерное количество.

Полетит только то, что нужно.

Полетит только то, что нужно и туда, куда нужно. А «туда, куда нужно» обеспечивается вот этой маской. В маске они застревают, не проникают в глубину фоторезистивной пластины, а в открытые участки пластины они проникают и формируют активную область.

А вот этот фотошаблон, который используется в фотолитографии, он что из себя представляет чисто физически?

Физически это очень сложное устройство. По проекту 90 нанометров, это — произведение искусства. Иногда один шаблон – это стекло размером примерно 157 на 157 миллиметров, толщиной порядка 6 микрон. На нем нанесен этот рисунок. Напыляются различные металлы, такими же методами фотолитографии, лазерами, различными способами формируется этот рисунок. Это стекло, через которое идет поляризованный свет. Но так как там уже есть различные оптические эффекты, эффекты близости двух элементов и так далее, то выглядит это немного не так, как рисунок. Это можно сравнить с искусством Дали, где из мелких фрагментов формируется общая картина. Дали использовал именно оптические эффекты, в том числе близости, для того, чтобы формировать такие сложные элементы. Сейчас это действительно произведение искусства, которое стоит приличных денег, порядка 15000 евро стоит один шаблон.

Из себя он представляет обычную стеклянную пластину, но она еще закрывается пеликлами, чтобы пыль не попала, или если и попала, то не так была критична. Фактически это стекло…Стеклышко с рисунком, но произвести его очень сложно.

Стеклышко непростое. Вы уже упомянули существующие на «Микроне» 180 нанометров, 90 нанометров, а также существующие на других производствах 65, 45 и т.д. Я знаю, есть технология 22 нанометра. Вы сказали, что разница в том размере элементов, которые можно создать на пластине. А где предел, где все это остановится? Я имею в виду традиционную кремниевую технологию.

Я думаю, что никто не сможет сказать, где все это остановится. Давно уже, 25 лет назад, велись споры о том, какая будет фотолитография, рентгеновская или лазером будем рисовать, а не на шаблонах… Все определяется, в-основном, доступностью материалов и экономикой. Кварцевый песок – наиболее доступный на нашей матушке-земле материал. Я думаю, его возможности далеко не исчерпаны. Сейчас уже 22 нанометра заявляют, Intel первый – 32 нанометра запускает, дальше идут разработки уже 18 и т.д. Я думаю, здесь скорее будет вопрос о технологиях и оборудовании, которое будет использовано для этого, а не с точки зрения каких-то новых материалов. Ближайшие 10-15 лет кремний будет и дальше хорошо существовать.

То есть, технологических ограничений нет, я правильно понимаю?