Аннотация: Рассматривается принцип действия дешифраторов на положительной и отрицательной логике.

Дешифратор является частным случаем преобразователей произвольных кодов, рассмотренных в

«Преобразователи произвольных кодов»

.

Дешифратор — это логическая схема, преобразующая двоичный код в унарный, когда только на одном из всех выходов появляется активный сигнал. Номер этого активного выхода в десятичном коде совпадает с двоичным кодом, подаваемым на входные линии дешифратора.

Принцип действия дешифратора лежит в основе работы всем известного устройства — домофона. Когда мы набираем номер на домофоне, звонок звенит только в одной квартире с указанным номером.

Рассмотрим схему дешифратора на три входа. Как при синтезе логической схемы по арифметическому выражению (

«Преобразователи произвольных кодов»

), составляем таблицу истинности. Поскольку в нашем примере у схемы должно быть три входа, количество комбинаций на этих входах будет равно

В соответствии с принципом синтеза логических схем по заданной формуле, после составления таблицы истинности нужно для каждого выхода написать логическое выражение. В данном случае задача упрощается, так как для каждого выхода логическая 1 имеет место быть только в одной строке таблицы. Поэтому в логическом выражении для каждого выхода будет только один минтерм:

|

( 4.1) |

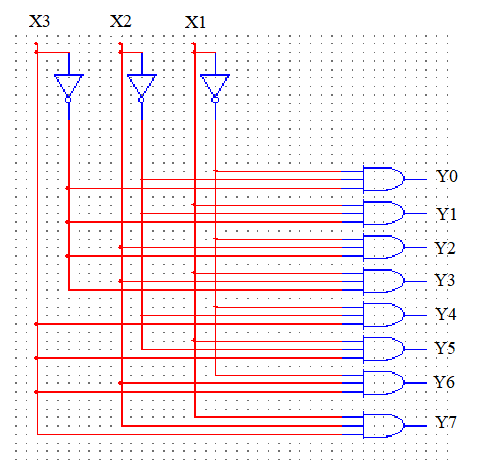

На рис. 4.1 показана функциональная схема данного дешифратора, соответствующая логическим выражениям (4.1).

В реальных дешифраторах обязательно присутствует входной управляющий сигнал, разрешающий работу данного дешифратора в соответствии со своей функцией. В простейшем случае разрешающий сигнал

Все рассмотренные ранее логические элементы могут быть реализованы в виде отдельных интегральных микросхем (ИМС) малой степени интеграции. Так, сборка из четырёх 2-входовых элементов И-НЕ объединяется в одном корпусе ИС К155ЛА3 [4].

Интегральная микросхема (ИМС) — микроэлектронное изделие, выполняющее определенную функцию преобразования и обработки сигнала и имеющее высокую плотность упаковки электрически соединённых элементов, которое рассматривается как единое целое [4, с.9].

Степень интеграции ИМС — показатель степени сложности микросхемы, характеризующийся числом содержащихся в ней элементов и компонентов [4, с.10]:

где

Различают интегральные микросхемы малой ( МИС — малые интегральные схемы), средней ( СИС ), большой ( БИС ) и сверхбольшой ( СБИС ) степени интеграции.

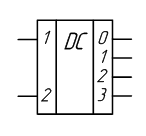

На рис. 4.3 показаны примеры условного графического обозначения (УГО) дешифраторов с активным единичным уровнем входных и выходных сигналов. Здесь и далее на УГО выделяется три поля. Центральное поле содержит обозначение функции, выполняемой ИМС. В данном случае это DC — от англ. D e c oder — дешифратор. Левое поле содержит обозначение входов ИМС, правое — обозначение выходов.

Рис.

4.3.

УГО дешифраторов с активными единичными входными и выходными сигналами: а — на один вход; б — на два входа; в — на три входа; г — на четыре входа.

При принятии отрицательной логики, когда активным уровнем всех сигналов является логический ноль, таблица истинности дешифратора на три входа (табл. 4.2) будет содержать в диагонали не единицы, а нули. При этом порядок следования комбинаций входных сигналов в данном случае удобно сделать обратным — в первой строке указать комбинацию

Активный нулевой уровень сигнала принято обозначать на УГО в виде инверсных входов и выходов так, как представлено на рис. 4.4. Поскольку в каждом столбце табл. 4.2 присутствует один ноль и семь единиц, логическое выражение удобнее представить в виде соответствующих макстермов:

|

( 4.2) |

Федеральное

агентство связи

Ордена

Трудового Красного Знамени федеральное

государственное бюджетное образовательное

учреждение высшего образования

«Московский

технический университет связи и

информатики»

ПРАКТИЧЕСКАЯ

РАБОТА №3

«Дешифратор»

Выполнили:

студенты гр. «Сортирный Союз»

лох

чмо

чукча

Бригада

№ 1

Проверила: Воронкова

М.Н.

Москва

2021

1.Цель

работы

Ознакомиться

с основными характеристиками интегральных

преобразователей кодов, получение

навыков проектирования дешифраторов.

Изучить связь между шифратором и

дешифратором. Научиться строить

дешифраторы и анализировать его работу.

2.Выполнение

1.

По данной таблице истинности дешифратора

(декодера) составить для него систему

уравнений и начертить блок-схему на

логических элементах

Таблица

истинности дешифратора для задания №

1

|

Входы |

Выходы |

|||||||||

|

X3 |

X2 |

X1 |

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

По

таблице истинности дешифратора можно

записать уравнения:

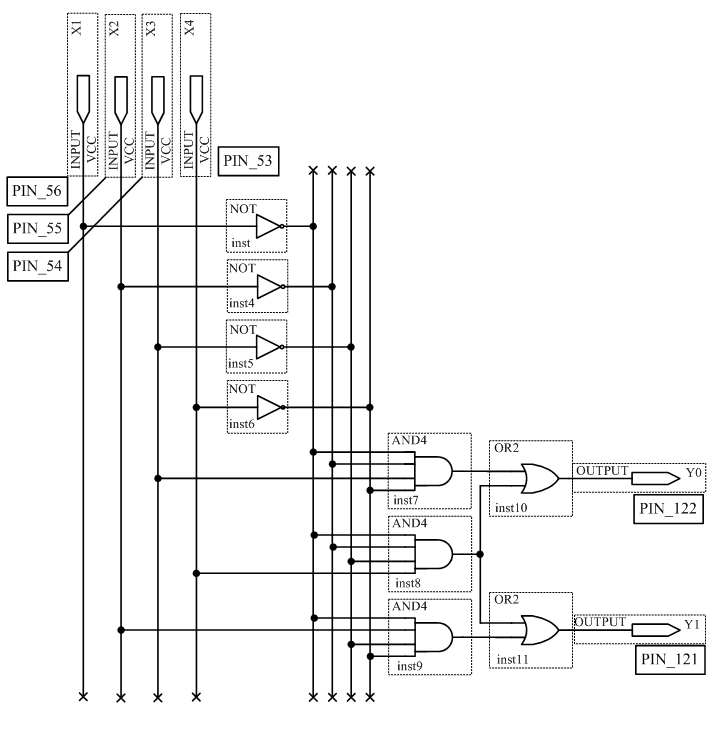

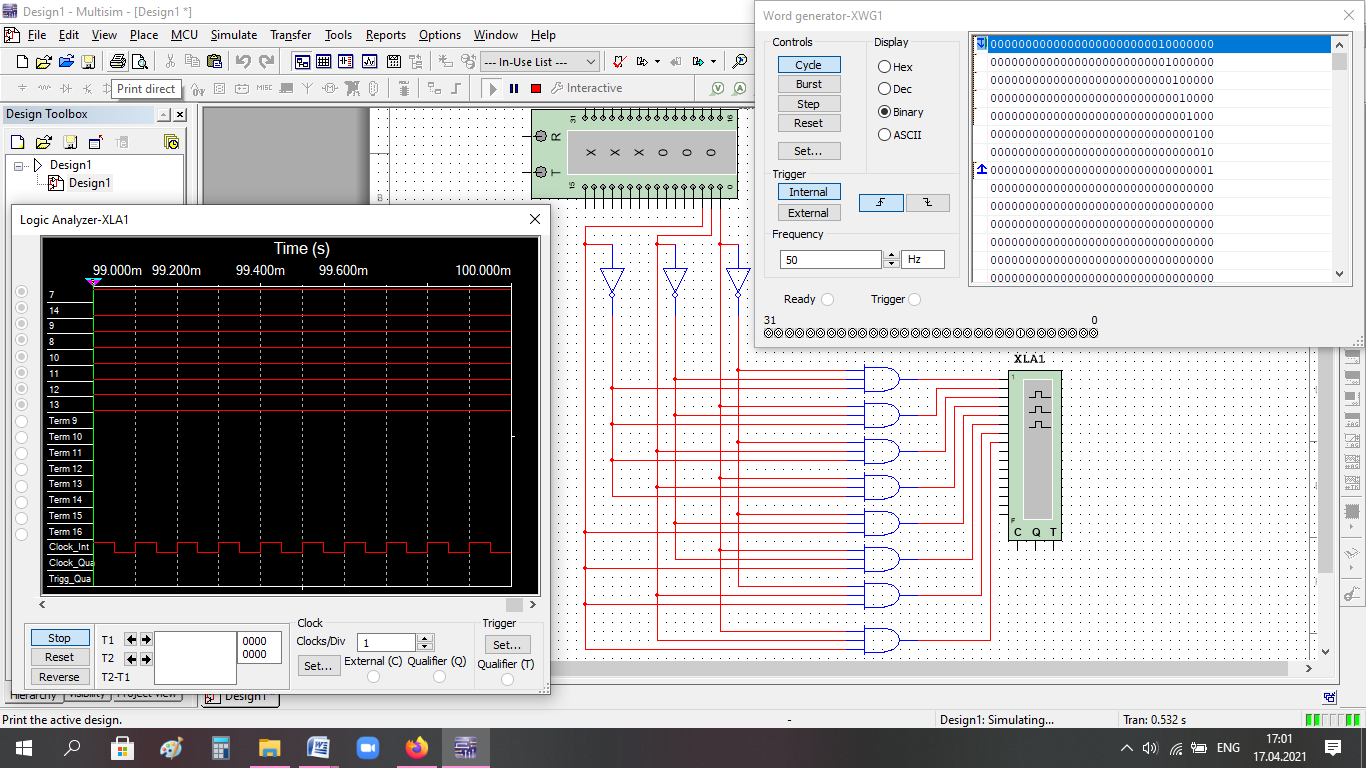

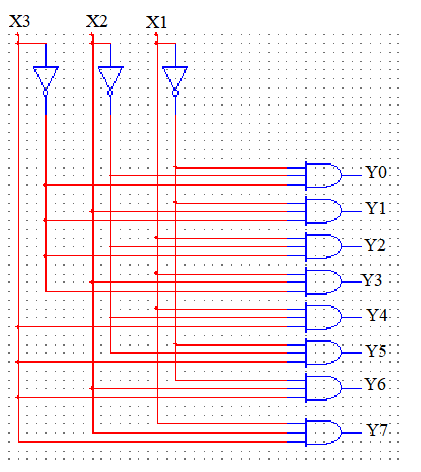

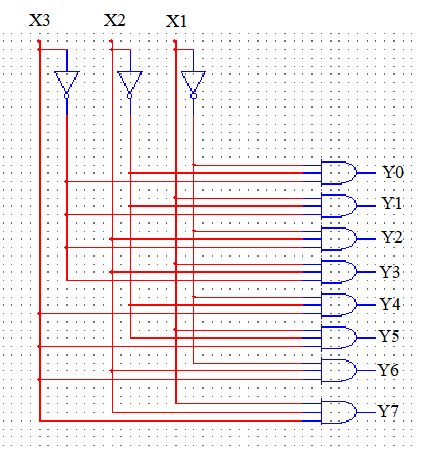

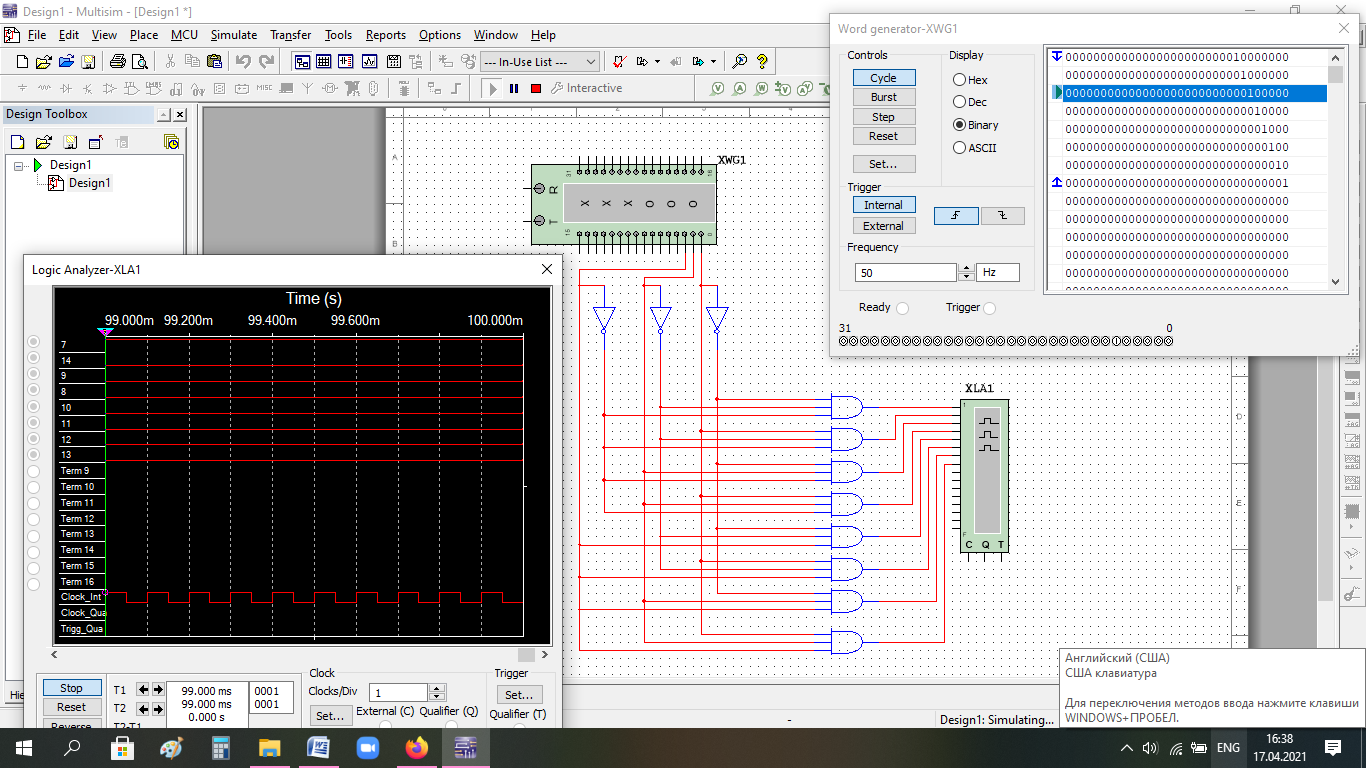

Блок-схема

на логических элементах

Логическая

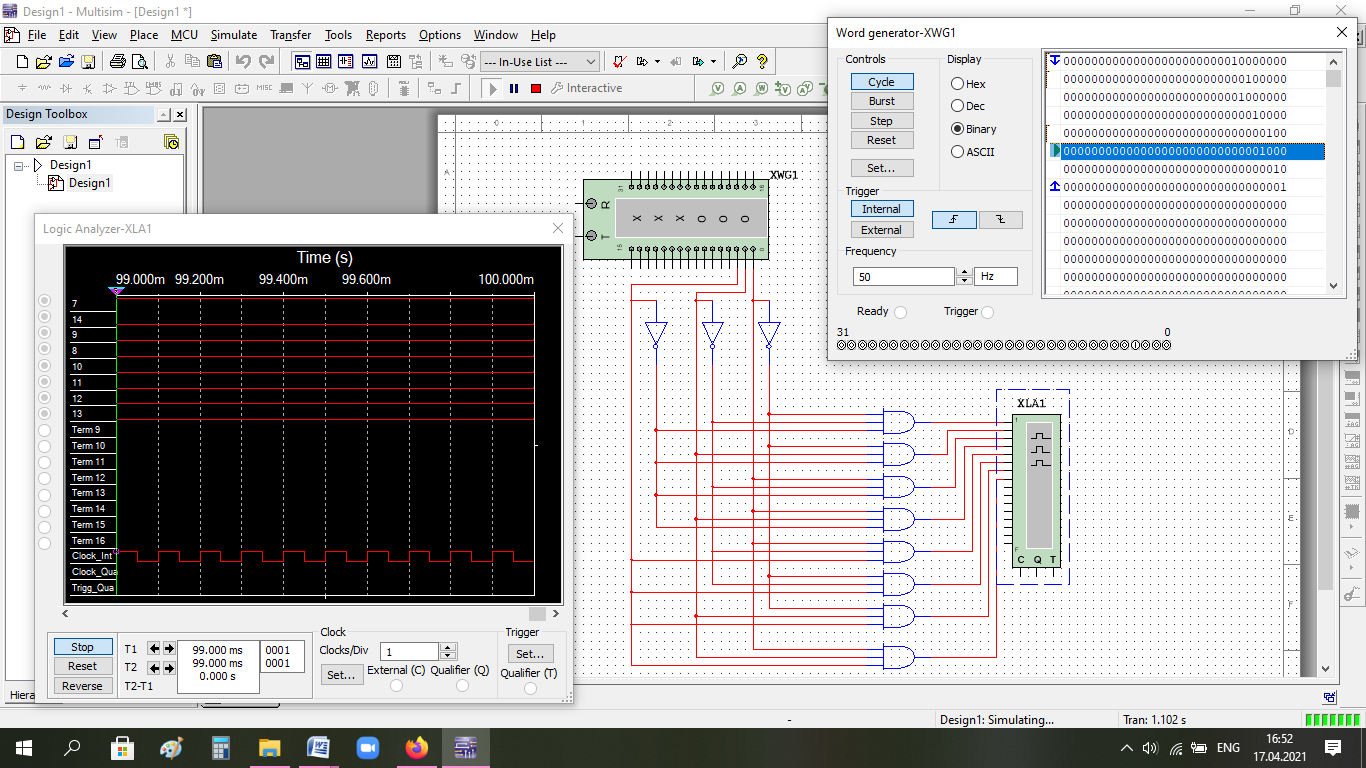

схема дешифратора задания № 1 в программе

Multisim

2.

По данной таблице истинности дешифратора

(декодера) составить для него систему

уравнений и начертить блок-схему на

логических элементах

Таблица

истинности дешифратора для задания №

2

|

Входы |

Выходы |

|||||||||

|

X3 |

X2 |

X1 |

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

По

таблице истинности дешифратора можно

записать уравнения:

Блок-схема

на логических элементах

Логическая

схема дешифратора задания № 2 в программе

Multisim

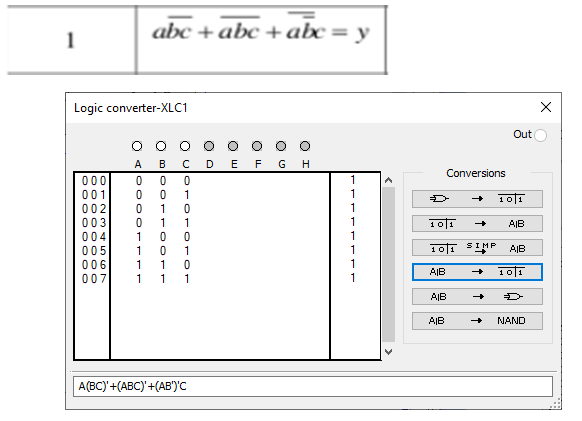

3.

Согласно заданию №1 практической работы

1 взять булеву функцию и ее таблицу

истинности, построить таблицу истинности

дешифратора, составить для него систему

уравнений и начертить блок-схему на

логических элементах.

Булева

функция и таблица истинности

из 1 задание практической работы №1

Таблица

истинности дешифратора для задания №

3

|

Входы |

Выходы |

|||||||||

|

X3 |

X2 |

X1 |

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

По

таблице истинности дешифратора можно

записать уравнения:

Блок-схема

на логических элементах

Логическая

схема дешифратора задания № 3 в программе

Multisim

3.Вывод

В

результате выполнения данной лабораторной

работы изучены основные характеристики

интегральных преобразователей кодов,

получены навыки проектирования

дешифраторов.

Изучена

связь между шифратором и дешифратором.

Получены

навыки построения и анализа работы

дешифраторов.

1 Цель работы

Целью работы является изучение принципов действия комбинационных схем: дешифратора, шифратора, преобразователя кода для семисегментного индикатора, мультиплексора, сумматора.

2 Краткие теоретические сведения

2.1 Дешифратор (декодер)

Дешифратор (декодер) служит для преобразования n-разрядного позиционного двоичного кода в единичный выходной сигнал на одном из 2n выходов. При каждой входной комбинации сигналов на одном из выходов появляется 1. Таким образом, по единичному сигналу на одном из выходов можно судить о входной кодовой комбинации. Таблица истинности для декодера с двумя входами изображена в таблице 2.1.

Таблица 2.1 – Таблица истинности двухразрядного дешифратора

| x1 | x2 | y0 | y1 | y2 | y3 |

| 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 |

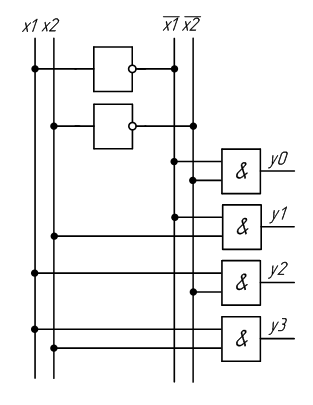

Для построения схемы декодера по таблице истинности воспользуемся методикой, изложенной в лабораторной работе №1, выполняемой на стенде LESO2. Например, устройство должно иметь 4 выхода. Для каждого выхода записываем логическое выражение. На основе СДНФ:

y0 = x1·x2

y1 = x1·x2

y2 = x1·x2

y3 = x1·x2

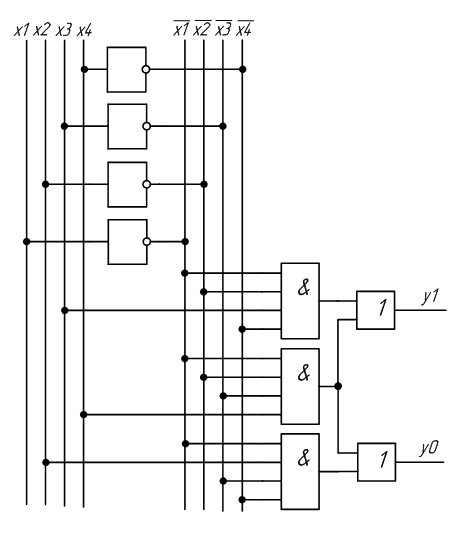

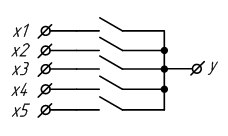

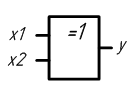

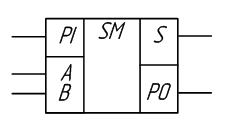

По этой системе выражений несложно построить схему требуемого дешифратора (рисунок 2.1).

Рисунок 2.1 – Схема дешифратора

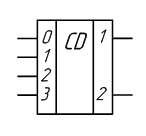

Условное графическое обозначение такого дешифратора изображено на рисунке 2.2.

Рисунок 2.2 – Условное графическое обозначение дешифратора

2.2 Шифратор (кодер)

Шифратор выполняет функцию, обратную декодеру (дешифратору), то есть преобразует непозиционный (унитарный) двоичный 2n разрядный код в n разрядный позиционный код. При подаче на один из входов единичного сигнала на выходе формируется соответствующий двоичный код. Составим таблицу истинности шифратора при n = 2.

Таблица 2.2 – Таблица истинности шифратора при n = 2

| x1 | x2 | x3 | x4 | y1 | y0 |

| 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 0 | 0 | 1 | 1 | 1 |

Синтезируем шифратор. Для этого запишем систему его собственных функций:

y1 = x1 · x2 · x3 · x4 + x1 · x2 · x3 ·x4

y0 = x1 · x2 · x3 · x4 + x1 · x2 · x3 ·x4

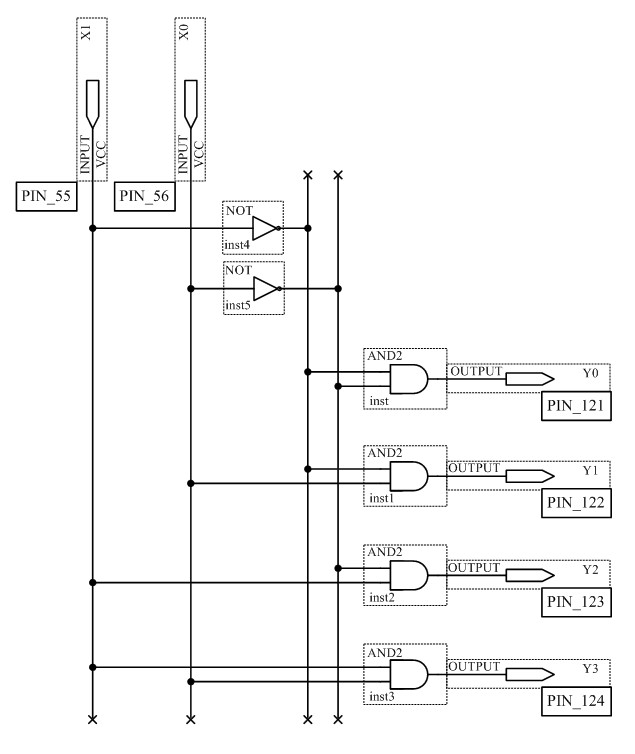

Рисунок 2.3 – Схема шифратора

Рисунок 2.4 – Условное графическое обозначение шифратора

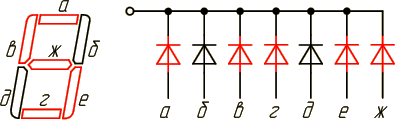

2.3 Преобразователь кода для семисегментного индикатора

Наиболее широко преобразователи кодов известны применительно к цифровым индикаторам. Например, преобразователь 4-х разрядного позиционного двоичного кода в десятичные цифры. Имеется семи сегментный индикатор и с его помощью требуется высветить десять цифр.

Рисунок 2.5 – Семи сегментный индикатор

Очевидно, что двоичный код должен иметь не менее 4 — х разрядов (2^4 = 16, что больше 10). Составим таблицу истинности работы такого преобразователя.

Таблица 2.3 – Таблица истинности преобразователя

| Цифра | Двоичный код 8-4-2-1 | a | б | в | г | д | е | ж | |||

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 3 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 4 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 5 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 6 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 7 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 8 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 9 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

По ТИ несложно составить систему собственных функций для всех выходов, т.е. СДНФ, минимизировать её и составить принципиальную схему.

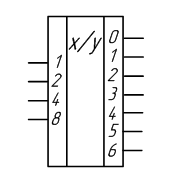

Рисунок 2.6 – Условное графическое обозначение преобразователя кода

2.4 Мультиплексор

Мультиплексор – устройство, которое позволяет коммутировать один из 2^n информационных входов X на один выход Y под действием n управляющих (адресных) сигналов. На рисунке. 2.7 изображена упрощенная функциональная схема мультиплексора на идеализированных электронных ключах.

Рисунок 2.7 – Схема мультиплексора на идеализированных электронных ключах

В цифровых схемах требуется управлять ключами при помощи логических уровней. Поэтому желательно подобрать устройство, которое могло бы выполнять функции электронного ключа с управлением цифровым сигналом. Попробуем «заставить» работать в качестве электронного ключа уже знакомые нам логические элементы. Рассмотрим ТИ логического элемента «И». При этом один из входов логического элемента «И» будем рассматривать как информационный вход электронного ключа, а другой вход – как управляющий. Так как оба входа логического элемента «И» эквивалентны, то не важно какой из них будет управляющим входом. Пусть вход X будет управляющим, а Y – информационным. Для простоты рассуждений, разделим ТИ на две части в зависимости от уровня логического сигнала на управляющем входе X.

Таблица 2.4 – Таблица истинности

| y | x | Out |

| 0 0 |

0 1 |

0 0 |

| 1 1 |

0 1 |

0 1 |

По таблице истинности отчётливо видно, что если на управляющий вход X подан нулевой логический уровень, сигнал, поданный на вход Y, на выход Out не проходит. При подаче на управляющий вход X логической единицы, сигнал, поступающий на вход Y, появляется на выходе Out. Это означает, что логический элемент «И» можно использовать в качестве электронного ключа. При этом не важно, какой из входов элемента «И» будет использоваться в качестве управляющего входа, а какой – в качестве информационного. Остается только объединить выходы элементов «И» на один общий выход. Это делается при помощи логического элемента «ИЛИ» точно так же как и при построении схемы по произвольной таблице истинности. Получившийся вариант схемы коммутатора с управлением логическими уровнями приведён на рисунке 2.8.

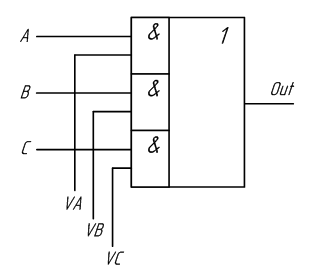

Рисунок 2.8 – Принципиальная схема мультиплексора, выполненная на логических элементах

В схемах, приведенных на рисунках 2.7 и 2.8, можно одновременно включать несколько входов на один выход. Однако обычно это приводит к непредсказуемым последствиям. Кроме того, для управления таким коммутатором требуется много входов, поэтому в состав мультиплексора обычно включают двоичный дешифратор, как показано на рисунке 2.9. Такая схема позволяет управлять переключением информационных входов мультиплексора при помощи двоичных кодов, подаваемых на его управляющие входы. Количество информационных входов в таких схемах выбирают кратным степени числа два.

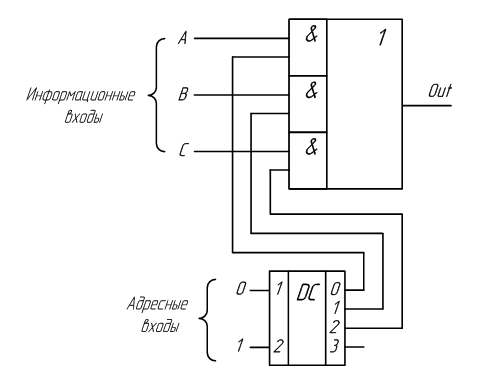

Рисунок 2.9 – Принципиальная схема мультиплексора, управляемого двоичным кодом

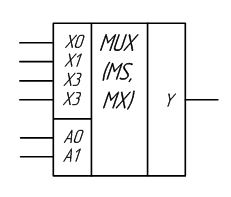

Условное графическое обозначение 4–х входового мультиплексора с управлением двоичным кодом приведено на рисунке 2.10. Входы A0 и A1 являются управляющими входами мультиплексора, определяющими адрес информационного входного сигнала, который будет соединён с выходным выводом мультиплексора Y. Информационные входные сигналы обозначены: X0, X1, X2 и X3.

Рисунок 2.10 – Условное графическое обозначение 4-х входового мультиплексора

В условном графическом обозначении названия информационных входов A, B, C и D заменены названиями X0, X1, X2 и X3, а название выхода Out заменено на название Y. Такое обозначение входов и выходов мультиплексора более распространено в отечественной литературе. Адресные входы обозначены как A0 и A1.

Об особенностях реализации мультиплесоров на языке Verilog можно почитать в статье:

Архитектура ПЛИС. Часть 2. Мультиплексор

2.5 Сумматор

Сумматор – узел компьютера, предназначенный для сложения двоичных чисел. Построение двоичных сумматоров обычно начинается с сумматора по модулю 2.

Сумматор по модулю 2

Схема сумматора по модулю 2 совпадает со схемой исключающее «ИЛИ».

Таблица 2.5 – Таблица истинности сумматора по модулю 2

| x1 | x2 | y |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Логическое выражение, описывающее сумматор по модулю 2:

y = x1 · x2 + x1 · x2

Рисунок 2.11 – Условное графическое обозначение сумматора по модулю 2

На основе логического уравнения, описывающего этот элемент можно синтезировать схему:

Рисунок 2.12 – Схема сумматора по модулю 2

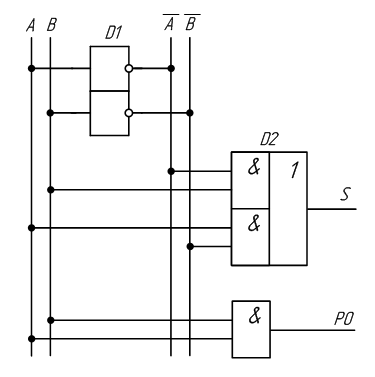

Сумматор по модулю 2 выполняет суммирование без учёта переноса. В обычном двоичном сумматоре требуется учитывать перенос, поэтому требуются схемы, позволяющие формировать перенос в следующий двоичный разряд. Таблица истинности такой схемы, называемой полусумматором, приведена в таблице 2.6.

Таблица 2.6 – Таблица истинности полусумматора

| A | B | S | P0 |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

Здесь A и B – слагаемые;

S – сумма;

P0 – перенос в старший разряд (выход переноса Pout).

Запишем систему собственных функций для полусумматора:

S = A · B + A · B

P0 = A · B

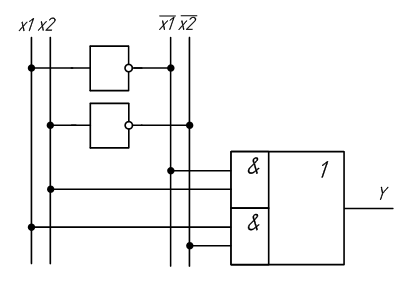

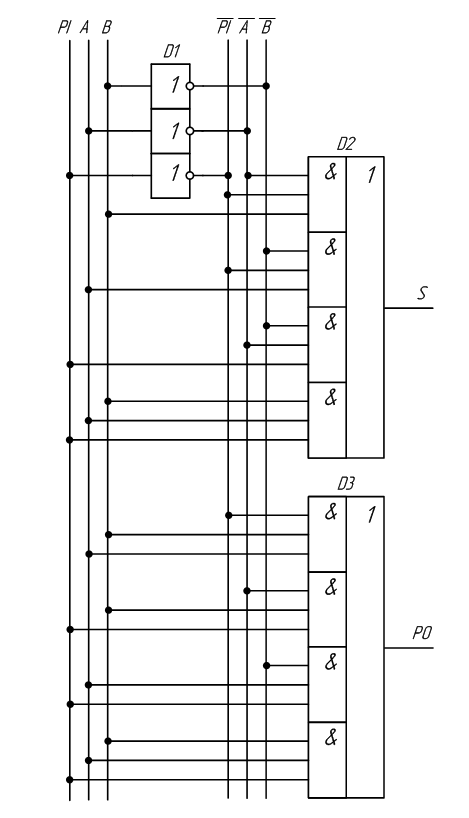

Рисунок 2.13 – Принципиальная схема, реализующая таблицу истинности полусумматора

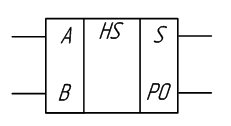

Рисунок 2.14 – Изображение полусумматора на схемах

Полный сумматор.

Схема полусумматора формирует перенос в старший разряд, но не может учитывать перенос из младшего разряда. При сложении многоразрядных двоичных чисел необходимо складывать три цифры в каждом разряде – 2 слагаемых и единицу переноса из предыдущего разряда PI.

Таблица 2.7 – Таблица истинности полного сумматора

| PI | A | B | S | PO |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

PI – вход 1 переноса из предыдущего разряда,

PO – выход 1 переноса в старший разряд.

На основании таблицы истинности запишем систему собственных функций для каждого выхода:

S = A · B · PI + A · B · PI + A · B · PI + A · B · PI

PO = A · B · PI + A · B · PI + A · B · PI + A · B · PI

В результате получим схему полного сумматора (рисунок 2.15).

Рисунок 2.15 – Принципиальная схема, реализующая таблицу истинности полного двоичного одноразрядного сумматора

Рисунок 2.16 – Изображение полного двоичного одноразрядного сумматора на схемах

3 Задание к работе

3.1 Исследовать принцип работы дешифратора 2 x 4

Сконфигурировать ПЛИС в соответствии с рисунком 3.1. Подключить к входам X0 и X1 переключатели S7 и S8, а к выходам Y0, Y1, Y2, Y3 светодиодные индикаторы LED5, LED6, LED7, LED8. Для этого подключить входы и выходы дешифратора к соответствующим ножкам ПЛИС.

Рисунок 3.1 – Схема дешифратора

Подавая все возможные комбинации логических уровней на входы X0, X1 с помощью ключей S7, S8 и наблюдая за состояниями светодиодных индикаторов LED5, LED6, LED7, LED8, заполните таблицу истинности дешифратора.

Таблица 3.1 – Таблица дешифратора

| x1 | x2 | y0 | y1 | y2 | y3 |

| 0 | 0 | ||||

| 0 | 1 | ||||

| 1 | 0 | ||||

| 1 | 1 |

3.2 Исследовать принцип работы шифратора 4×2

Сконфигурировать ПЛИС в соответствии с рисунком 3.2.

Рисунок 3.2 – Схема шифратора 4×2

Подключить к входам X1, X2, X3, X4 переключатели S8, S7, S6, S5, а к выходам Y0, Y1 светодиодные индикаторы LED8, LED7. Для этого подключить входы и выходы дешифратора к соответствующим ножкам ПЛИС. Подавая все возможные комбинации логических уровней на входы X1, X2, X3, X4 с помощью ключей S8, S7, S6, S5 и наблюдая за состояниями светодиодных индикаторов LED7, LED8, заполните таблицу истинности шифратора.

Таблица 3.2 – Таблица истинности шифратора

| x1 | x2 | x3 | x4 | y1 | y0 |

| 1 | 0 | 0 | 0 | ||

| 0 | 1 | 0 | 0 | ||

| 0 | 0 | 1 | 0 | ||

| 0 | 0 | 0 | 1 |

3.3 Исследовать работу преобразователя кода для семисегментного индикатора.

Составить таблицу истинности преобразователя кода (таблица. 3.3).

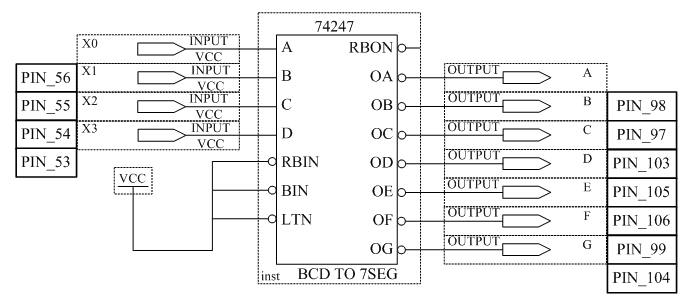

Собрать схему, изображенную на рисунке 3.3.

Таблица 3.3 – Таблица истинности преобразователя

| x3 | x2 | x1 | x0 | A | B | C | D | E | F | G |

| 0 | 0 | 0 | 0 | |||||||

| 0 | 0 | 0 | 1 | |||||||

| 0 | 0 | 1 | 0 | |||||||

| 0 | 0 | 1 | 1 | |||||||

| 0 | 1 | 0 | 0 | |||||||

| 0 | 1 | 0 | 1 | |||||||

| 0 | 1 | 1 | 0 | |||||||

| 0 | 1 | 1 | 1 | |||||||

| 1 | 0 | 0 | 0 | |||||||

| 1 | 0 | 0 | 1 |

Рисунок 3.3 – Схема преобразователя кода для семисегментного индикатора

Подавая с помощью ключей S8, S7, S6, S5 различные кодовые комбинации на входы X0, X1, X2, X3 определить цифры, высвечиваемые на индикаторе. По результатам эксперимента заполнить таблицу 3.4.

Таблица 3.4 – Таблица, описывающая работу преобразователя кода для семисегментного индикатора

| x3 | x2 | x1 | x0 | Показание индикатора |

| 0 | 0 | 0 | 0 | |

| 0 | 0 | 0 | 1 | |

| 0 | 0 | 1 | 0 | |

| 0 | 0 | 1 | 1 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 0 | 1 | |

| 0 | 1 | 1 | 0 | |

| 0 | 1 | 1 | 1 | |

| 1 | 0 | 0 | 0 | |

| 1 | 0 | 0 | 1 |

3.4 Исследовать работу мультиплексора 4×1

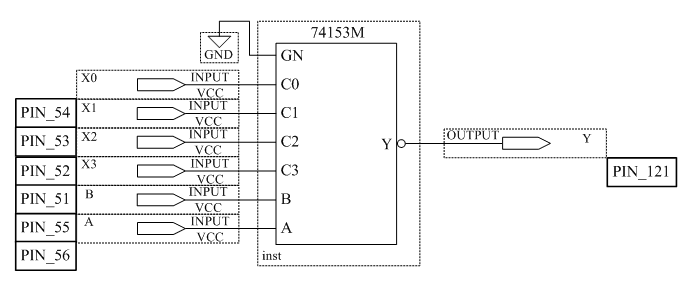

Сконфигурировать ПЛИС в соответствии с рисунком 3.4.

Рисунок 3.4 – Схема мультиплексора 4×1

Поочередно устанавливая все возможные кодовые комбинации на адресных входах A и B, определите номера коммутируемых каналов. Номер коммутируемого канала определяется путем поочерёдного подключения к входам X0, X2, X3, X4 уровня логической единицы и наблюдения за выходом Y. Заполните таблицу 3.5.

Таблица 3.5 – Таблица, описывающая работу мультиплексора

| B | A | Номер коммутируемого канала |

| 0 | 0 | |

| 0 | 1 | |

| 1 | 0 | |

| 1 | 1 |

3.5 Исследовать схему сумматора

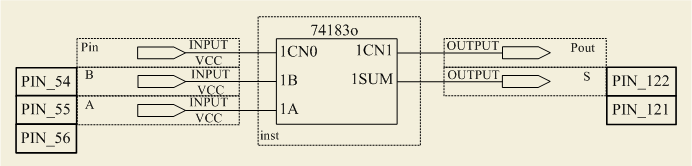

Сконфигурировать ПЛИС в соответствии с рисунком 3.5. Здесь Pin, Pout соответственно вход и выход единицы переноса, A и B – слагаемые, S – сумма.

Рисунок 3.5 – Схема сумматора

Заполнить таблицу истинности сумматора (таблица 3.6).

Таблица 2.7 – Таблица истинности полного сумматора

| Pin | B | A | Pout |

| 0 | 0 | 0 | |

| 0 | 0 | 1 | |

| 0 | 1 | 0 | |

| 0 | 1 | 1 | |

| 1 | 0 | 0 | |

| 1 | 0 | 1 | |

| 1 | 1 | 0 | |

| 1 | 1 | 1 |

4 Содержание отчета

- Цель работы.

- Схемы исследования дешифратора, шифратора, преобразователя кода для семисегментного индикатора, мультиплексора, сумматора.

- Таблицы истинности для каждой схемы.

- Выводы по каждому заданию.

5 Контрольные вопросы

- Принцип работы дешифратора?

- Как синтезировать дешифратор с произвольной разрядностью?

- Как работает шифратор?

- Изобразите таблицу истинности шифратора.

- Как работает преобразователь кода для семисегментного индикатора?

- Как устроен семи сегментный индикатор?

- Как работает мультиплексор?

- Как в лабораторной работе проводилось исследование мультиплексора?

- Как работает сумматор?

- Изобразите таблицу истинности шифратора.

- Что такое единица переноса?

Практическая

работа №9

«Исследование

работы дешифратора»

Цель работы: познакомиться с

принципами построения и работой дешифраторов на базе логических элементов.

Теоретические сведения.

Дешифраторы

Дешифратор

(decoder) это логическая схема с несколькими входами и несколькими выходами,

которая преобразует кодированные входные сигналы в кодированные выходные сигналы,

причем входной и выходной коды различны. Входной код обычно имеет меньшее число

разрядов, чем выходной, и между входным и выходным кодовыми словами имеется

взаимно-однозначное соответствие.

В общем случае

дешифратор имеет n однофазных входов и m выходов, где n -разрядность

дешифруемого кода.

Дешифратора с числом выходов 2n m = называется полным.

Существуют

следующие классификации дешифраторов:

· по способу

структурной организации:

§ одноступенчатые,

§ многоступенчатые,

· по формату

входного кода:

§ двоичные,

§ двоично-десятичные,

· по разрядности

дешифруемого кода:

§ 2-разрядные,

§ 3-разрядные,

§ и т.д.

· по форме подачи входного

кода:

§ с однофазными

входами,

§ с парафазными

входами,

· по количеству

входов:

§ полные

дешифраторы,

§ неполные

дешифраторы,

· по типу

используемых логических элементов:

§ И-НЕ,

§ ИЛИ-НЕ,

§ И-ИЛИ-НЕ.

В схему

дешифраторов встраиваются один или два стробирующих (разрешающих) входа W ,

с помощью которых определяется момент срабатывания дешифратора. Кроме того

сигналы W могут быть использованы для наращивания разрядности входного

кода. На практике из n входов и m выходов называется «из n в

m ».

Многоступенчатые

дешифраторы

Принцип построения

многоступенчатых дешифраторов состоит в последовательном разбиении входного

многоразрядного кода для получения в каждой группе двух-трех разрядов. После

этого многоступенчатая схема дешифратора изображается в виде соединения ряда

линейных схем.

Рис. 1. Примеры разбиения

входного дешифруемого кода на группы.

преобразует код на его входах в сигнал только на одном из выходов. Часто применяется

для преобразования двоичного кода в десятичный. Таблица истинности и

обозначение показаны на рисунке.

Рис. 2. Примеры схема дешифратора и

таблица истинности.

Математическая

запись работы дешифратора следующая:

Для его реализации

необходимы логические элементы «НЕ» и «И».

Рассмотрим

подробнее функцию дешифратора.

В

стандартные серии входят дешифраторы на 4 выхода (2 разряда входного кода), на

8 выходов (3 разряда входного кода) и на 16 выходов (4 разряда входного кода).

Они обозначаются соответственно как 2–4, 3–8, 4–16. Различаются микросхемы

дешифраторов входами управления (разрешения/запрета выходных сигналов), а также

типом выхода: 2С или ОК. Выходные сигналы всех дешифраторов имеют отрицательную

полярность. Входы, на которые поступает входной код, называют часто адресными

входами. Обозначают эти входы 1, 2, 4, 8, где число соответствует весу

двоичного кода (1 — младший разряд, 2 — следующий разряд и т.д.), или А0, А1,

А2, А5. В отечественных сериях микросхемы дешифраторов обозначаются буквами ИД.

На рис. 3 показаны три наиболее типичных микросхемы дешифраторов.

Рис. 3. Примеры микросхем

дешифраторов

Код на

входах 1, 2, 4, 8 определяет номер активного выхода (вход 1 соответствует

младшему разряду кода, вход 8 — старшему разряду кода). Входы разрешения С1,

С2, С3 объединены по функции И и имеют указанную на рисунке полярность. Для

примера в табл. 5.1 приведена таблица истинности дешифратора ИД7 (3—8).

Существуют и дешифраторы 4–10 (например, ИД6), которые обрабатывают не все

возможные 16 состояний входного кода, а только первые 10 из них.

Первые

три строки таблицы соответствуют запрету выходных сигналов. Разрешением выхода

будет единица на входе С1 и нули на входах С2 и С5. Символ ―Х‖ обозначает

безразличное состояние данного входа (неважно, нуль или единица). Нижние восемь

строк соответствуют разрешению выходных сигналов. Номер активного выхода (на

котором формируется нулевой сигнал) определяется кодом на входах 1, 2, 4,

причем вход 1 соответствует младшему разряду кода, а вход 4 — старшему разряду

кода.

Наиболее типичное применение

дешифраторов состоит именно в дешифрировании входных кодов, при этом входы С

используются как стробирующие, управляющие сигналы. Номер активного (то есть

нулевого) выходного сигнала показывает, какой входной код поступил. Если нужно

дешифровать код с большим числом разрядов, то можно объединить несколько

микросхем дешифраторов (пример показан на рис.4).

Рис.

4. Увеличение количества разрядов дешифратора

Модель

схемы дешифратора

Микросхема

логики TTL 74155 является полным аналогом ИМС К155ИД4 (с которой вы будете

иметь дело в практической реализации).

ИМС К155ИД4 содержит два дешифратора 2→4 с объединѐнными адресными

входами А и B и раздельными входами стробирования С и G (см. рис.6).

Рис.

6 – УГО К155ИД4

Разрешающей

комбинацией для одного дешифратора является наличие лог. «0» на обоих входах

системы 0 E , а для другого – лог. «1» на одном и лог. «0» на другом входе

схемы 0 E .

Сборка

дешифратора на беспаичной макетной плате

Постановка задачи:

Необходимо собрать схему дешифратора,

подавая на входы различные комбинации сигналов, проверить соответствие таблице

переключений выходных сигналов для этих схем.

Порядок

выполнения работы.

1.

Изучить

теоретические сведения о дешифраторе.

2.

Отобразить

в рабочих тетрадях схему дешифратора и таблицу переключений.

3.

Начертить

в схемном редакторе схему проверить работу устройства.

Варианты

заданий.

1.

Исследование линейного двухвходового дешифратора.

1. Соберите схему линейного двухвходового

дешифратора на элементах И-НЕ. Входные сигналы подавайте с выхода счетчика,

построенного на JK-триггерах.

Наблюдайте сигналы на выходе.

2. Постройте таблицу истинности

дешифратора.

3. Увеличивая частоту, наблюдайте, что

происходит в работе дешифратора.

4. Рассмотрите схему, изображенную на

рисунке. Здесь используется линия задержки из трех элементов для того, чтобы

разрешающий сигнал пришел на все элементы И-НЕ в тот момент, когда на них уже

будут сформированы правильные сигналы.

5. Наблюдайте

сигналы на выходе.

6. Определите с

помощью осциллографа время задержки.

Задание 2.

По таблице

истинности построить принципиальную схему дешифратора.

|

Входы |

Выходы |

|||||||||

|

8 |

4 |

2 |

1 |

a |

b |

c |

d |

e |

f |

g |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

|

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

|

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

Пример.

Таблица

истинности десятичного дешифратора.

|

Входы |

Выходы |

||||||||||||

|

8 |

4 |

2 |

1 |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

Принципиальная схема десятичного дешифратора.

Отчет

должен содержать:

1. Краткая

теоретическая часть.

2. Этапы

выполнения работы.

3.

Выводы

о проделанной работе.

Контрольные

вопросы

1. Что такое дешифратор?

2. Для чего нужны дешифраторы?

3. Какие классификации дешифраторов вы знаете?

4. При решении, каких задач цифровой техники

используются дешифраторы?

5.Составить схему дешифратора на два входа и четыре выхода.