Аннотация: Рассматривается принцип действия триггеров как простейших элементов электронной памяти.

Цифровое устройство называется последовательностным [1, с.91], если его выходные сигналы зависят не только от текущих значений входных сигналов, но и от последовательности значений входных сигналов, поступивших на входы в предшествующие моменты времени. Поэтому говорят, что такие функциональные узлы «обладают памятью».

Триггер — это логическая схема с положительной обратной связью, которая может находиться только в одном из двух устойчивых состояний, принимаемых за состояние логического нуля и логической единицы.

В отличие от всех рассмотренных ранее комбинационных схем, работа которых определяется только входными сигналами, состояние триггера в текущий момент зависит и от его состояния в предыдущий момент времени. Иными словами, триггер — это схема с запоминанием [2].

RS-триггеры

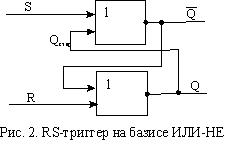

Простейшая функциональная схема RS — триггера в базисе ИЛИ-НЕ приведена на рис. 7.1,а. Здесь

Рис.

7.1.

RS-триггер в базисе ИЛИ-НЕ: а — функциональная схема; б — УГО

Очевидно, при наличии двух входных сигналов, возможны 4 варианта работы схемы (табл. 7.1). Начнем анализ с состояний, когда на один из входов подается решающий для элемента ИЛИ-НЕ сигнал логической 1.

Первая такая комбинация:

Вторая комбинация:

Если на оба входа подать

дет через положительную обратную связь подан на верхний элемент ИЛИ-НЕ и состояние

Рассмотрим последнюю, четвертую комбинацию входных сигналов:

Для рассматриваемой схемы характерно также и то, что оба элемента триггера переключаются не одновременно, а последовательно друг за другом. Поэтому в ходе переходного процесса переключения триггера в противоположное состояние будут моменты времени, когда и на прямом, и на инверсном выходах будут одинаковые уровни. Это недопустимо по определению, поскольку триггер должен быть либо в устойчивом состоянии логического

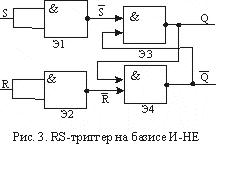

Функциональная схема простейшего триггера в базисе И-НЕ показана на рис. 7.2.а. Поскольку для функции И-НЕ решающим является сигнал логического нуля, активный уровень входных сигналов будет нулевым (табл. 7.2), что отражается на УГО триггера (рис. 7.2,б) в виде инверсного изображения входов

Рис.

7.2.

RS-триггер в базисе И-НЕ: а — функциональная схема; б — УГО

Синхронный RS-триггер

Основное назначение триггера в цифровых схемах — хранить выработанные логическими схемами результаты. Для отсечения еще не установившихся, искаженных переходными процессами результатов между выходом какой-либо логической схемы и входами триггера ставят ключи в виде элементов И-НЕ. Действие этого сигнала аналогично разрешающему сигналу

«Функциональные узлы комбинаторной логики. Дешифраторы»

). На первый и второй логические элементы И-НЕ одновременно поступает синхросигнал

Рис.

7.3.

Синхронный RS-триггер: а — функциональная схема; б — УГО

Недостатком схемы остается наличие недопустимой комбинации на входе, при которой получается неустойчивое состояние схемы.

Триггеры

Триггеры предназначены для

запоминания двоичной информации.

Использование триггеров позволяет

реализовывать устройства оперативной

памяти (то есть памяти, информация в

которой хранится только на время

вычислений). Однако триггеры могут

использоваться и для построения некоторых

цифровых устройств с памятью, таких как

счётчики,

преобразователи

последовательного кода в параллельный

или цифровые линии задержки.

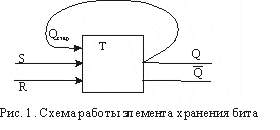

Простейшая схема, позволяющая

запоминать двоичную информацию, может

быть построена на двух инверторах,

охваченных положительной обратной

связью. Эта схема приведена на рисунке 1.

Рисунок 1. Схема простейшего

триггера, построенного на инверторах.

В этой схеме может быть только

два состояния — на выходе Q присутствует

логическая

единица и на выходе Q присутствует

логический

ноль. Если логическая единица

присутствует на выходе Q, то на инверсном

выходе будет присутствовать логический

ноль, который после очередного

инвертирования подтверждает уровень

логической единицы на выходе Q. И наоборот,

если на выходе Q присутствует логический

ноль, то на инверсном выходе будет

присутствовать логическая единица.

Такая ситуация будет сохраняться

до тех пор пока включено питание. Но вот

вопрос — а как записывать в такой триггер

информацию? Нам потребуются входы записи

нуля и записи единицы.

RS-триггеры

RS-триггер получил название по

названию своих входов. Вход S (Set –

установить англ.) позволяет устанавливать

выход триггера Q в единичное состояние.

Вход R (Reset – сбросить англ.) позволяет

сбрасывать выход триггера Q (Quit – выход

англ.) в нулевое состояние.

Для реализации RS-триггера

воспользуемся логическими элементами

“2И-НЕ”. Его принципиальная схема

приведена на рисунке 2.

Рисунок 2. Схема простейшего

триггера на схемах «И». Входы R и S

инверсные (активный уровень’0′).

Рассмотрим работу изображенной

на рисунке 2 схемы подробнее. Пусть

на входы R и S подаются единичные

потенциалы. Если на выходе верхнего

логического элемента “2И-НЕ” Q присутствует

логический ноль, то на выходе нижнего

логического элемента “2И-НЕ” появится

логическая единица. Эта единица подтвердит

логический ноль на выходе Q. Если на

выходе верхнего логического элемента

“2И-НЕ” Q первоначально присутствует

логическая единица, то на выходе нижнего

логического элемента “2И-НЕ” появится

логический ноль. Этот ноль подтвердит

логическую единицу на выходе Q. То есть

при единичных входных уровнях схема

RS-триггера работает точно так же как и

схема на инверторах.

Подадим на вход S нулевой

потенциал. Согласно таблице истинности

логического элемента “И-НЕ” на выходе

Q появится единичный потенциал. Это

приведёт к появлению на инверсном выходе

триггера нулевого потенциала. Теперь,

даже если снять нулевой потенциал с

входа S, на выходе триггера останется

единичный потенциал. То есть мы записали

в триггер логическую единицу.

Точно так же можно записать в

триггер и логический ноль. Для этого

следует воспользоваться входом R. Так

как активный уровень на входах оказался

нулевым, то эти входы — инверсные. Составим

таблицу истинности RS-триггера. Входы R

и S в этой таблице будем использовать

прямые, то есть запись нуля, и запись

единицы будут осуществляться единичными

потенциалами (таблица 1).

Таблица 1. Таблица истинности

RS-триггера.

|

R |

S |

Q(t) |

Q(t+1) |

Пояснения |

|

0 |

0 |

0 |

0 |

Режим |

|

0 |

0 |

1 |

1 |

|

|

0 |

1 |

0 |

1 |

Режим |

|

0 |

1 |

1 |

1 |

|

|

1 |

0 |

0 |

0 |

Режим |

|

1 |

0 |

1 |

0 |

|

|

1 |

1 |

0 |

* |

R=S=1 |

|

1 |

1 |

1 |

* |

RS-триггер можно построить и на

логических элементах «ИЛИ». Схема

RS-триггера, построенного на логических

элементах «ИЛИ» приведена на рисунке

3. Единственное отличие в работе этой

схемы будет заключаться в том, что сброс

и установка триггера будет производиться

единичными логическими уровнями. Эти

особенности связаны с принципами работы

инверсной логики, которые рассматривались

ранее.

Рисунок 3. Схема простейшего

триггера на схемах «ИЛИ». Входы R и

S прямые (активный уровень ‘1’).

Так как RS-триггер при построении

его на логических элементах “И” и “ИЛИ”

работает одинаково, то его изображение

на принципиальных схемах тоже одинаково.

Условно-графическое изображение

RS-триггера на принципиальных схемах

приведено на рисунке 4.

Рисунок 4. Условно-графическое

обозначение RS-триггера.

Синхронные RS-триггеры.

Схема RS-триггера позволяет

запоминать состояние логической схемы,

но так как в начальный момент времени

может возникать переходный процесс (в

цифровых схемах этот процесс называется

опасные гонки), то запоминать состояния

логической схемы нужно только в

определённые моменты времени, когда

все переходные процессы закончены.

Это означает, что большинство

цифровых схем требуют сигнала синхронизации

(тактового сигнала). Все переходные

процессы в комбинационной логической

схеме должны закончиться за время

периода синхросигнала, подаваемого на

входы триггеров. Триггеры, запоминающие

входные сигналы только в момент времени,

определяемый сигналом синхронизации,

называются синхронными. Для того чтобы

отличать от них рассмотренные ранее

варианты (RS-триггер и триггер Шмитта)

эти триггеры получили название

асинхронных.

Формировать синхронизирующие

сигналы с различной частотой и скважностью

при помощи генераторов и одновибраторов

мы уже научились в предыдущих главах.

Теперь научимся записывать в триггеры

входные логические сигналы только при

наличии разрешающего сигнала.

Для этого нам потребуется

схема, пропускающая входные сигналы

только при наличии синхронизирующего

сигнала. Такую схему мы уже использовали

при построении схем мультиплексоров и

демультиплексоров. Это логический

элемент “И”. Триггеры, записывающие

сигналы только при наличии синхронизирующего

сигнала называются синхронными.

Принципиальная схема синхронного

RS-триггера приведена на рисунке 5.

Для таких цифровых схем требуются

синхронные триггеры. Схема синхронного

триггера приведена на рисунке 4, а

обозначение на принципиальных схемах

на рисунке 5.

Рисунок 5. Схема синхронного

RS-триггера, построенного на элементах

«И-НЕ».

В таблице 2 приведена таблица

истинности синхронного RS-триггера. В

этой таблице символ x означает, что

значения логических уровней на данном

входе не важны. Они не влияют на работу

триггера.

Таблица 2. Таблица истинности

синхронного RS-триггера.

|

С |

R |

S |

Q(t) |

Q(t+1) |

Пояснения |

|

0 |

x |

x |

0 |

0 |

Режим |

|

0 |

x |

x |

1 |

1 |

|

|

1 |

0 |

0 |

0 |

0 |

Режим |

|

1 |

0 |

0 |

1 |

1 |

|

|

1 |

0 |

1 |

0 |

1 |

Режим |

|

1 |

0 |

1 |

1 |

1 |

|

|

1 |

1 |

0 |

0 |

0 |

Режим |

|

1 |

1 |

0 |

1 |

0 |

|

|

1 |

1 |

1 |

0 |

* |

R=S=1 |

|

1 |

1 |

1 |

1 |

* |

Как мы уже показали в предыдущей

главе, RS-триггеры могут быть реализованы

на различных элементах. При этом логика

их работы не изменяется. В то же самое

время триггеры часто выпускаются в виде

готовых микросхем (или реализуются

внутри БИС в виде готовых модулей),

поэтому на принципиальных схемах

синхронные триггеры обычно изображаются

в виде условно-графических обозначений.

Условно-графическое обозначение

синхронного RS-триггера приведено на

рисунке 6.

Рисунок 6. Условно-графическое

обозначение синхронного RS-триггера.

D-триггеры

В RS-триггерах для записи

логического нуля и логической единицы

требуются разные входы, что не всегда

удобно. При записи и хранении данных

один бит может принимать значение, как

нуля, так и единицы. Для его передачи

достаточно одного провода. Как мы уже

видели ранее, сигналы установки и сброса

триггера не могут появляться одновременно,

поэтому можно объединить эти входы при

помощи инвертора, как показано на рисунке

1.

Рисунок 1. Схема D-триггера

(защелки)

Такой триггер получил название

D-триггер. Название происходит от

английского слова delay — задержка.

Конкретное значение задержки определяется

частотой следования импульсов

синхронизации. Условно-графическое

обозначение D-триггера на принципиальных

схемах приведено на рисунке 2.

Рисунок 2. Условно-графическое

обозначение D-триггера (защелки)

Таблица истинности D-триггера

достаточно проста, она приведена в

таблице 1. Как видно из этой таблицы,

этот триггер способен запоминать по

синхросигналу и хранить один бит

информации.

Таблица 1. Таблица истинности

D-триггера

|

С |

D |

Q(t) |

Q(t+1) |

Пояснения |

|

0 |

x |

0 |

0 |

Режим |

|

0 |

x |

1 |

1 |

|

|

1 |

0 |

x |

0 |

Режим |

|

1 |

1 |

x |

1 |

Нужно отметить, что отдельный

инвертор при реализации триггера на

ТТЛ элементах не нужен, так как самый

распространённый элемент ТТЛ логики —

это «2И-НЕ». Принципиальная схема

D-триггера на элементах 2И-НЕ” приведена

на рисунке 9.

Ещё проще реализуется D-триггер

на КМОП логических элементах. В КМОП

микросхемах вместо логических элементов

“И” используются обычные транзисторные

ключи. Схема D-триггера приведена на

рисунке 10.

Рисунок 10. Схема D-триггера,

реализованная на КМОП элементах

При подаче высокого уровня

синхросигнала C транзистор VT1 открывается

и обеспечивает передачу сигнала с входа

D на инверсный выход Q через инвертор

D1. Транзистор VT2 при этом закрыт и

отключает второй инвертор, собранный

на транзисторах VT2 и VT3. При подаче низкого

потенциала на вход C включается второй

инвертор, который вместе с инвертором

D1 и образует триггер.

Во всех рассмотренных ранее

схемах синхронных триггеров синхросигнал

работает по уровню, поэтому триггеры

называются триггерами, работающими по

уровню. Ещё одно название таких триггеров,

пришедшее из иностранной литературы —

триггеры-защёлки. Легче всего объяснить

появление этого названия по временной

диаграмме, приведенной на рисунке 11.

Рисунок 11. Временная диаграмма

D-триггера (защелки)

По этой временной диаграмме

видно, что триггер-защелка хранит данные

на выходе только при нулевом уровне на

входе синхронизации. Если же на вход

синхронизации подать активный высокий

уровень, то напряжение на выходе триггера

будет повторять напряжение, подаваемое

на вход этого триггера.

Входное напряжение запоминается

только в момент изменения уровня

напряжения на входе синхронизации C

с высокого уровня на низкий уровень.

Входные данные как бы «защелкиваются»

в этот момент, отсюда и название –

триггер-защелка.

Принципиально в этой схеме

входной переходной процесс может

беспрепятственно проходить на выход

триггера. Поэтому там, где это важно,

необходимо сокращать длительность

импульса синхронизации до минимума.

Чтобы преодолеть такое ограничение

были разработаны триггеры, работающие

по фронту.

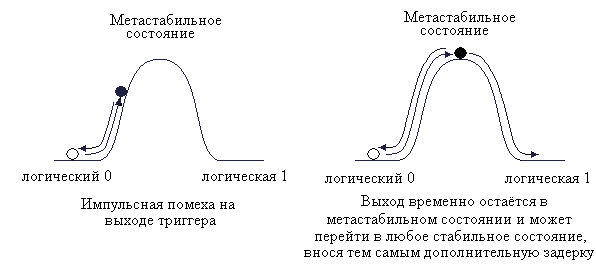

Явление метастабильности.

До сих пор мы предполагали, что

сигнал на входе триггера может принимать

только два состояния: логический ноль

и логическая единица. Однако синхроимпульс

может прийти в любой момент времени, в

том числе и в момент смены состояния

сигнала на входе триггера.

Если синхросигнал попадёт

точно на момент перехода входным сигналом

порогового уровня, то триггер на некоторое

время может попасть в неустойчивое

метастабильное состояние, при котором

напряжение на его выходе будет находиться

между уровнем логического нуля и

логической единицы. Это может привести

к нарушению правильной работы цифрового

устройства.

Состояние метастабильности

триггера подобно неустойчивому состоянию

шарика, находящегося на вершине

конического холма. Такая ситуация

иллюстрируется рисунком 1. Обычно триггер

не может долго находиться в состоянии

метастабильности и быстро возвращается

в одно из стабильных состояний. Время

нахождения в метастабильном состоянии

зависит от уровня шумов схемы и

использованной технологии изготовления

микросхем.

Рисунок 1. Иллюстрация явления

метастабильности.

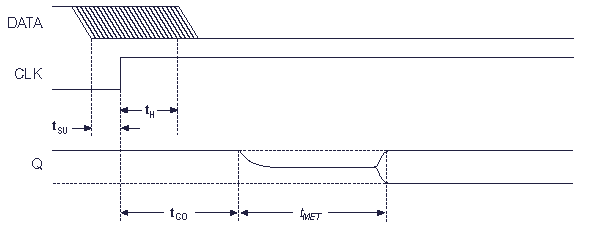

Временные параметры триггера

в момент возникновения состояния

метастабильности и выхода из этого

состояния приведены на рисунке 2. Время

tSU (register setup time or tSU) на

этом рисунке это минимальное время

перед синхроимпульсом, в течение которого

логический уровень сигнала должен

оставаться стабильным для того, чтобы

избежать метастабильности выхода

триггера. Время tH (register hold time or tH)

это минимально необходимое время

удержания стабильного сигнала на входе

триггера для того, чтобы избежать

метастабильности его выхода. Время

состояния метатастабильности случайно

и зависит от многих параметров. На

рисунке 2 оно обозначено tMET.

Рисунок 2. Иллюстрация явления

метастабильности.

Вероятность того, что время

метастабильности превысит заданную

величину, экспоненциально уменьшается

с ростом времени, в течение которого

выход триггера находится в метастабильном

состояние.

где t – это коэффициент обратно

пропорциональный коэффициенту усиления

и полосе пропускания элементов, входящих

в состав триггера.

Склонность триггеров к

метастабильности обычно оценивается

величиной, обратной скорости отказов.

Это значение выражается как интервал

времени между отказами. Его можно

определить по формуле:

где

t0 = tSU – tH

fс

– тактовая частота

fd

– частота с которой меняются входные

данные

Для того чтобы можно было

оценить эту величину, приведём таблицу

для двух микросхем. Последняя строчка

этой таблицы эквивалентна времени

метастабильности tMET = 5 нс.

Таблица 3. Сравнительные

характеристики КМОП и Bi-КМОП триггеров

|

Условия |

SN74ACT |

SN74ABT |

|

fc |

8400 лет |

8.1*109 |

|

fc |

92 дня |

1400 лет |

|

fc |

— |

2 часа |

Метастабильное состояние не

всегда приводит к неправильной работе

цифрового устройства. Если время ожидания

устройства после прихода импульса

синхронизации достаточно велико, то

триггер может успеть перейти в устойчивое

состояние, и мы даже ничего не заметим.

То есть если мы будем учитывать время

метастабильности tmet то метастабильность

никак не скажется на работе остальной

цифровой схемы.

Если же это время будет

неприемлемым для работы схемы, то можно

поставить два триггера последовательно,

как это показано на рисунке 3. Это снизит

вероятность возникновения метастабильного

состояния.

Рисунок 3. Схема снижения

вероятности возникновения метастабильного

состояния на выходе триггера.

Для сравнения приведем MBTF для

новой схемы. Сравнение производится

тех же самых микросхем, что и в предыдущем

примере. Время метастабильности tMET

= 5 нс для 50МГц, tMET = 5 нс для 67МГц,

tMET = 5 нс для 80МГц.

Таблица 4. Сравнительные

характеристики КМОП и Bi-КМОП триггеров

|

Условия |

SN74ACT |

SN74ABT |

|

fc |

2.62*1028 |

4.77*1047 |

|

fc |

3,56*1019 |

2.18*1034 |

|

fc |

4.9*1010 |

1*1021 |

|

fc |

417 лет |

1.28*109 |

|

fc |

— |

2900 лет |

D-триггеры, работающие по

фронту.

Фронт сигнала синхронизации,

в отличие от высокого (или низкого)

потенциала, не может длиться продолжительное

время. В идеале длительность фронта

равна нулю. Поэтому в триггере, запоминающем

входную информацию по фронту не нужно

предъявлять требования к длительности

тактового сигнала.

Триггер, запоминающий входную

информацию по фронту, может быть построен

из двух триггеров, работающих по

потенциалу. Сигнал синхронизации будем

подавать на эти триггеры в противофазе.

Схема такого триггера приведена на

рисунке 12.

Рисунок 12. Схема D-триггера,

работающего по фронту

Рассмотрим работу схемы

триггера, приведенной на рисунке 12

подробнее. Для этого воспользуемся

временными диаграммами, показанными

на рисунке 13. На этих временных

диаграммах обозначение Q΄ соответствует

сигналу на выходе первого триггера. Так

как на вход синхронизации второго

триггера тактовый сигнал поступает

через инвертор, то когда первый триггер

находится в режиме хранения, второй

триггер пропускает сигнал на выход

схемы. И наоборот, когда первый триггер

пропускает сигнал с входа схемы на свой

выход, второй триггер находится в

режиме хранения.

Рисунок 13. Временные диаграммы

D-триггера.

Обратите внимание, что сигнал

на выходе всей схемы в целом не зависит

от сигнала на входе «D» схемы. Если

первый триггер пропускает сигнал данных

со своего входа на выход, то второй

триггер в это время находится в режиме

хранения и поддерживает на выходе

предыдущее значение сигнала, то есть

сигнал на выходе схемы тоже не может

измениться.

В результате проведённого

анализа временных диаграмм мы определили,

что сигнал в схеме, приведенной на

рисунке 12 запоминается только в

момент изменения сигнала на синхронизирующем

входе «C» с единичного потенциала

на нулевой.

Динамические D-триггеры

выпускаются в виде готовых микросхем

или входят в виде готовых блоков в

составе больших интегральных схем,

таких как базовый матричный кристалл

(БМК) или программируемых логических

интегральных схем (ПЛИС).

Условно-графическое обозначение

D-триггера, запоминающего информацию

по фронту тактового сигнала, приведено

на рисунке 12.

Рисунок 14. Условно-графическое

обозначение D-триггера.

То, что триггер запоминает

входной сигнал по фронту, отображается

на условно-графическом обозначении

треугольником, изображённым на выводе

входа синхронизации. То, что внутри

этого триггера находится два триггера,

отображается в среднем поле

условно-графического изображения

двойной буквой T.

Иногда при изображении

динамического входа указывают, по какому

фронту триггер (или триггеры) изменяет

своё состояние. В этом случае используется

обозначение входа, как это показано на

рисунке 15.

Рисунок 8.18. Обозначение

динамических входов

На рисунке 8.18 а обозначен

динамический вход, работающий по

переднему (нарастающему) фронту сигнала.

На рисунке 8.18 б обозначен динамический

вход, работающий по заднему (спадающему)

фронту сигнала.

Промышленностью выпускаются

готовые микросхемы, содержащие

динамические триггеры. В качестве

примера можно назвать микросхему

1533ТМ2. В этой микросхеме содержится

сразу два динамических триггера. Они

изменяют своё состояние по переднему

фронту сигнала синхронизации.

T-триггеры

Т-триггер – это счетный триггер.

У Т-триггера имеется только один вход.

После поступления на этот вход импульса,

состояние Т-триггера меняется на прямо

противоположное. Счётным он называется

потому, что он как бы подсчитывает

количество импульсов, поступивших на

его вход. Жаль только, что считать этот

триггер умеет только до одного. При

поступлении второго импульса T-триггер

снова сбрасывается в исходное состояние.

Т-триггеры строятся только на

базе двухступенчатых триггеров, подобных

рассмотренному ранее D-триггеру.

Использование двух триггеров позволяет

избежать самовозбуждения схемы, так

как счетные триггеры строятся при помощи

схем с обратной связью

Т-триггер можно синтезировать

из любого двухступенчатого триггера.

Рассмотрим пример синтеза Т-триггера

из динамического D-триггера. Для того

чтобы превратить D-триггер в счётный,

необходимо ввести цепь обратной связи

с инверсного выхода этого триггера на

вход, как показано на рисунке 1.

Рисунок 1. Схема T-триггера,

построенная на основе D-триггера.

Временная диаграмма T-триггера

приведена на рисунке 2. При построении

этой временной диаграммы был использован

триггер, работающий по заднему фронту

синхронизирующего сигнала.

Рисунок 2. Временные диаграммы

T-триггера.

Т-триггеры используются при

построении схем различных счётчиков,

поэтому в составе БИС различного

назначения обычно есть готовые модули

этих триггеров. Условно-графическое

обозначение T-триггера

приведено на рисунке 3.

Рисунок 3. Условно-графическое

обозначение T-триггера.

JK-триггеры

Прежде чем начать изучение

JK-триггера, вспомним принципы работы

RS-триггера. Напомню, что в этом триггере

есть запрещённые комбинации входных

сигналов. Одновременная подача единичных

сигналов на входы R и S запрещены. Очень

хотелось бы избавиться от этой неприятной

ситуации.

Таблица истинности JK-триггера

практически совпадает с таблицей

истинности синхронного RS-триггера. Для

того чтобы исключить запрещённое

состояние, схема триггера изменена

таким образом, что при подаче двух единиц

JK-триггер превращается в счётный триггер.

Это означает, что при подаче на тактовый

вход C импульсов JK-триггер изменяет своё

состояние на противоположное. Таблица

истинности JK-триггера приведена в

таблице 1.

Таблица 1. Таблица истинности

JK-триггера.

|

С |

K |

J |

Q(t) |

Q(t+1) |

Пояснения |

|

0 |

x |

x |

0 |

0 |

Режим |

|

0 |

x |

x |

1 |

1 |

|

|

1 |

0 |

0 |

0 |

0 |

Режим |

|

1 |

0 |

0 |

1 |

1 |

|

|

1 |

0 |

1 |

0 |

1 |

Режим |

|

1 |

0 |

1 |

1 |

1 |

|

|

1 |

1 |

0 |

0 |

0 |

Режим |

|

1 |

1 |

0 |

1 |

0 |

|

|

1 |

1 |

1 |

0 |

1 |

K=J=1 |

|

1 |

1 |

1 |

1 |

0 |

Один из вариантов внутренней

схемы JK-триггера приведен на рисунке

1.

Рисунок 1. Внутренняя схема

JK-триггера.

Для реализации счетного режима

в схеме, приведенной на рисунке 8.22,

введена перекрестная обратная связь с

выходов второго триггера на входы R и S

первого триггера. Благодаря этой обратной

связи на входах R и S никогда не может

возникнуть запрещенная комбинация.

Приводить временные диаграммы

работы JK-триггера не имеет смысла, так

как они совпадают с приведёнными ранее

диаграммами RS- и T-триггера. Условно-графическое

обозначение JK-триггера приведено на

рисунке 2.

Рисунок 2. Условно-графическое

обозначение JK-триггера.

На этом рисунке приведено

обозначение типовой цифровой микросхемы

JK-триггера, выполненной по ТТЛ технологии.

В промышленно выпускающихся микросхемах

обычно кроме входов JK-триггера реализуются

входы RS-триггера, которые позволяют

устанавливать триггер в заранее

определённое исходное состояние.

В названиях отечественных

микросхем для обозначения JK-триггера

присутствуют буквы ТВ. Например,

микросхема К1554ТВ9 содержит в одном

корпусе два JK-триггера. В качестве

примеров иностранных микросхем,

содержащих JK-триггеры можно назвать

такие микросхемы, как 74HCT73 или 74ACT109.

Так как JK-триггер является

универсальной схемой, то рассмотрим

несколько примеров использования этого

триггера. Начнем с примера использования

JKтриггера в качестве обнаружителя

коротких импульсов.

Рисунок 3. Схема обнаружения

короткого импульса.

В данной схеме при поступлении

на вход “C” импульса триггер переходит

в единичное состояние, которое затем

может быть обнаружено последующей

схемой (например, микропроцессором).

Для того, чтобы привести схему в исходное

состояние, необходимо подать на вход R

уровень логического нуля.

Теперь рассмотрим пример

построения на JK-триггере ждущего

мультивибратора. Один из вариантов

подобной схемы приведен на рисунке 4.

Рисунок 4. Схема ждущего

мультивибратора.

Схема работает подобно предыдущей

схеме. Длительность выходного импульса

определяется постоянной времени RC

цепочки. Диод VD1 предназначен для быстрого

восстановления исходного состояния

схемы (разряда емкости C). Если быстрое

восстановление схемы не требуется,

например, когда длительность выходных

импульсов гарантированно меньше половины

периода следования входных импульсов,

то диод VD1 можно исключить из схемы

ждущего мультивибратора.

В качестве последнего примера

применения универсального JK-триггера,

рассмотрим схему счетного T-триггера.

Схема счетного триггера приведена на

рисунке 5.

Рисунок 5. Схема счетного

триггера, построенного на JK-триггере.

В схеме, приведенной на рисунке

5, для реализации счетного режима работы

триггера на входы J и K подаются уровни

логической единицы.

RS-триггеры Триггером называют логическую схему с положительной обратной связью, имеющую два устойчивых состояния – единичное и нулевое, которые обозначаются соответственно 1 и 0 (рис.23.1, а). В основе любого триггера находится кольцо из двух инверторов (рис. 23.1, б, в). Триггер является элементом памяти последовательностных логических устройств, на схемах он обозначается буквой Т

При подаче питания в результате переходных процессов произвольно один из инверторов устанавливается в единичное состояние, а другой – в нулевое. В дальнейшем состояние логических элементов (ЛЭ) сохраняется, так как сигнал с выхода одного ЛЭ поддерживает состояние другого ЛЭ. Общепринято такую схему называть элементом памяти или защелкой.

Входы триггера разделяют на информационные и управляющие (вспомогательные). Это разделение в значительной степени условно.

Информационные входы используются для управления состоянием триггера. Управляющие входы обычно используются для предварительной установки триггера в некоторое состояние и для синхронизации. Как правило, триггеры имеют 2 выхода: прямой и инверсный.

Рис. 23.1. Структурная схема триггера

Триггеры классифицируют по способу приема информации, принципу построения и функциональным возможностям. По способу приема информации различают асинхронные и синхронные триггеры. Асинхронный триггер изменяет свое состояние непосредственно в момент появления соответствующего информационного сигнала.

Синхронные триггеры реагируют на информационные сигналы только при наличии соответствующего сигнала на так называемом входе синхронизации С (от англ. clock). Этот вход также обозначают терминами «строб», «такт».

Синхронные триггеры в свою очередь подразделяют на триггеры со статическим (статические) и динамическим (динамические) управлением по входу синхронизации С.

Статические триггеры воспринимают информационные сигналы при подаче на вход С логической единицы (прямой вход) или логического нуля (инверсный вход).

Динамические триггеры воспринимают информационные сигналы при изменении (перепаде) сигнала на входе С от 0 к 1 (прямой динамический С-вход) или от 1 к 0 (инверсный динамический С-вход).

По способу построения различают одно- и двухступенчатые триггеры. В одноступенчатом триггере имеется одна ступень запоминания информации, а в двухступенчатом – две такие ступени. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе. Двухступенчатый триггер обозначают ТТ.

По функциональным возможностям триггеры разделяют на следующие классы:

- — с раздельной установкой состояния 0 и 1 (RS-триггеры);

- — универсальные (JK-триггеры);

- — с приемом информации по одному входу D (D-триггеры, или триггеры задержки);

- — со счетным входом Т (Т-триггеры).

Входы триггеров обычно обозначают следующим образом:

- — S – вход для установки в состояние «1»;

- — R – вход для установки в состояние «0»;

- — J – вход для установки в состояние «1» в универсальном триггере;

- — К – вход для установки в состояние «0» в универсальном триггере;

- — Т – счетный (общий) вход;

- — D – вход для установки в состояние «1» или в состояние «0»;

- — V – дополнительный управляющий вход для разрешения приема информации (иногда используют букву Е вместо V).

Рассмотрим некоторые типы триггеров и их реализацию на логических элементах.

Условное графическое обозначение асинхронного RS-триггера и таблица его переходов приведены на рис. 23.2.

Рис. 23.2. RS-триггер

Триггер имеет два информационных входа: S (от англ. set) и R (от англ. reset). Закон функционирования триггеров удобно описывать таблицей переходов, которую иногда также называют таблицей истинности (рис. 23.2). Через St, Rt, Qt обозначены соответствующие логические сигналы, имеющие место в некоторый момент времени t, а через Qt+1 выходной сигнал в следующий момент времени t+1.

Комбинацию входных сигналов St = 1, Rt = 1 часто называют запрещенной, так как после нее триггер оказывается в состоянии (1 или 0), предсказать которое заранее невозможно. Подобных ситуаций нужно избегать.

Рассматриваемый триггер может быть реализован на двух элементах ИЛИ-НЕ (рис. 23.3,а) или И-НЕ (рис.23.3,б).

Эти схемы функционируют в полном соответствии приведенной выше таблицей переходов, которая на рис. 23.2 приведена в сокращенном виде. Полная таблица истинности (таблица переходов) RS-триггера на элементах ИЛИ-НЕ имеет следующий вид (рис. 23.4).

Рис. 23.3. RS-триггер на элементах ИЛИ-НЕ (а) и И-НЕ (б)

Рис. 23.4. Таблица истинности RS-триггера на элементах ИЛИ-НЕ

В асинхронном RS-триггере на элементах И-НЕ переключение производится логическим «0», подаваемым на вход R или S, т. е. реализуется обратная рассмотренной ранее таблице переходов (рис. 23.4). Запрещенная комбинация соответствует логическим «0» на обоих входах.

Микросхема К564ТР2 содержит 4 асинхронных RS-триггера и один управляющий вход (рис. 23.5). При подаче на вход V низкого уровня выходы триггеров отключаются от выводов микросхем и переходят в третье (высокоимпедансное) состояние. При подаче на вход V логического сигнала «1» триггеры работают в соответствии с вышеприведенной таблицей переходов.

Рассмотрим синхронный RS-триггер (рис. 23.6). Если на входе С – логический «0», то и на выходе верхнего входного элемента «И-НЕ», и на выходе нижнего будет логическая «1». А это, как отмечалось выше, обеспечивает хранение информации. Таким образом, если на входе С – логический «0», то воздействие на входы R, S не приводит к изменению состояния триггера. Если же на вход синхронизации С подана логическая единица, то схема реагирует на входные сигналы так же, как и рассмотренная ранее.

В рассмотренных выше RS-триггерах с обратными связями возможны неопределенности, обусловленные одновременным изменением информации на прямом и инверсном выходах, связанных с R и S входами. Для устранения этого эффекта применяются двухступенчатые триггеры.

При использовании двухступенчатого RS-триггера (рис.23.7) допускается соединение его входов и выходов. Двухступенчатый триггер состоит из двух синхронных RS-триггеров и дополнительного элемента НЕ. При подаче входных управляющих сигналов и синхросигнала (рис.23.8) производится запись информации в первый триггер (момент t1). При этом второй триггер не изменяет своего состояния, так как на его синхровход с инвертора подается логический ноль. Только по окончании записи в первый триггер при изменении синхросигнала с единицы на ноль производится запись во второй триггер двухступенчатой системы (t2).

Рис. 23.6. Синхронный RS-триггер

Рис. 23.7. Структурная схема двухступенчатого триггера

Рис. 23.8. Временная диаграмма работы двухступенчатого триггера

Таким образом, двухступенчатый триггер переключается по заднему фронту синхронизирующего импульса. Такая синхронизация называется динамической. Наличие динамической синхронизации отмечено наклонной чертой. Использование в триггере двух ступеней обозначается двумя буквами ТТ.

Рассмотрим в качестве примера RS-триггер типа 136ТР1 – синхронный триггер. Триггер имеет сложные входы R и S , вызывающие изменение состояния триггера при действии фронта синхроимпульса (перепадом с 0 на 1). Информационные входы R и S имеют входную логику «3И» (рис. 23.9).

Входы R и S (выводы 2 и 13) – установочные входы (установки 1 и 0 соответственно) действуют независимо, подан синхроимпульс или нет.

Рис. 23.9. Синхронный RS-триггер К136ТР1: а – УГО, б – таблица истинности

В таблице (рис. 23.10, б) приняты следующие обозначения:

Виды триггеров и особенности их работы

Содержание

- 1 Определение

- 2 Разновидности

- 2.1 Асинхронные

- 2.2 Синхронные

- 3 D-триггер

- 4 Т-триггер

- 4.1 Асинхронные

- 4.2 Синхронные

- 5 JK-триггер

- 6 Симметричный

- 7 Заключение

- 8 Видео по теме

Электроника предполагает точное выполнение заданной программы с учетом текущего состояния всей логической схемы. За часть работы электронной цепи отвечают триггеры. Статья опишет — основные типы триггеров, их устройство и принцип работы, а так же расскажет зачем такие устройства используются в электронных схемах. Отдельно будет описан симметричный триггер.

Определение

Что такое триггер? Триггером называют электронное устройство, обладающее способностью довольно долгое время находиться в 1-ом из 2-х стабильных состояний, а так же чередовать их из-за воздействия какого-то внешнего сигнала. Триггер — это по сути простая электроника, от которой зависит работоспособность более сложных систем

Он способен хранить двоичную информацию (ноль или один) после того, как перестанут действовать входные импульсы. Основное назначение устройства, это переключение из одного состояния в другое. Хранит триггер в своей памяти 1 бит информации, которые и определяют его текущее состояние: логический «0» или логическая «1».

Какие входы есть у триггера? Любой триггер может иметь несколько входов, которые бывают:

- Информационными. Они отвечают за общее состояние устройства в момент работы всей цепи.

- Управляющими. Отвечают за установку триггера в предварительное положение и за его дальнейшую синхронизацию.

Работа устройства строится на 2 элементах «И-НЕ», 2 «ИЛИ-НЕ» и других, некоторые разновидности триггеров работают на логических элементах КМОП, ТТЛ, ЭСЛ. Принцип работы любого триггера зависит от количества входов/выходов, а также от типа самого устройства.

В электронике используются устройства на транзисторах или микросхемах. Транзисторные модели применяются при сложных интегральных схемах старого типа. Логическая микросхема обладает меньшими габаритами, хранит информацию без перегрева и перегрузок. Поэтому их используют в более миниатюрных и сложных цепях современной электроники.

Разновидности

Для того чтобы разобраться как работает триггер, необходимо понять к какому классу и типу он относится. Существуют 2 основных класса этих устройств:

- Синхронные с двумя основными классами: статическими и динамическими.

- Асинхронные.

Обе разновидности имеют схожий принцип работы. Отличие заключается только в процессе перехода сигнала из одного состояния в другое. Асинхронные делают это напрямую, а синхронные работают исходя из этого сигнала.

Асинхронные

Асинхронные RS-триггер имеет 2 основных входа «R» и «S». Также предусматриваются выходы «Q» и «Q−». Устройство RS триггера позволяет выполнять следующую последовательность:

- Вход «S» является установочным. На него подается высокое напряжение, вследствие чего логический выход «Q» устанавливается как «1».

- Вход «R» отвечает за сброс положения. Высокое напряжение в виде логической «1» на этом входе предполагает установку 0 на выходе «Q», а на выходе «Q–» – «1».

Асинхронный RS-триггер условно работает следующим образом:

- При подаче напряжения на вход «S» устройство включается и хранит такое состояние даже при потере положительного сигнала.

- При подаче сигнала на вход «R» устройство отключается, при этом сохраняя логический 0 на выходах.

Схема RS-триггера асинхронного типа самая простая. Она работает без синхронизации с дополнительным входом. Используется RS компонент в простых элементах или как дополнение для более сложных триггеров.

Далее будет представлена УГО, таблица истинности и общая схема такого триггера.

Синхронные

Немного более сложное устройство. Работают с дополнительной синхронизацией сигналов. Эти RS-триггеры также имеют входы «R» и «S», а также выходы «Q» и «Q–». Отличие заключается в наличие синхронизирующего входа «С». Этот контакт нужен для синхронизации входящих сигналов. Называют этот вход «clock» или тактовый. Триггер имеет следующий принцип работы:

- Первоначально сигнал поступает к контакту входа «С» и проходит синхронизацию.

- С контакта «С» сигнал поступает на вход «S» в виде логической 1 или высокого напряжения.

- На «Q» устанавливается логическая 1, а сам цепь при этом включается.

Синхронизация используется для снижения части помех. Часто RS-триггеры этого типа используют для цепей с параллельным подключением, значительно снижая помехи от элементов с высокой магнитной индуктивностью.

Графическое обозначение, таблица истинности и диаграмма устойчивых состояний устройства представлена ниже.

Асинхронные и синхронные модели далеко не единственные, которые использует схемотехника для построения логических моделей работы. Далее будут представлены разновидности триггеров с иным принципом работы.

D-триггер

Эти виды простых триггеров так же используют для хранения информации о своем текущем состоянии один бит памяти. Используют его в простых электронных схемах вычислительных устройств и автоматики. Данная модель также относится к синхронному типу и имеет вход «С». Главное отличие заключается в замене 2 входов «R-S» на один контакт «D». Применение всего одного входа и наличие синхронизации позволяет значительно упростить работу устройства. Для работы D-триггера используется следующая схема:

- На контакт «С» поступает сигнал логической 1 или высокое напряжение.

- Сигнал проходит синхронизацию.

- Поступает на контакт входа D.

- Если выход «Q» находился в состоянии логической 1, то он включается.

- Если на выходе «Q» находился логический 0 или этот контакт находился в состоянии сброса, логическая 1 передается на выход «Q−».

Иными словами, состояние триггера на выходе зависит от его предыдущего положения. Если предыдущее положение было в состоянии высокого напряжения, то на этот выход поступит логическая 1. Если положение было в состоянии сброса, то логический 0.

Практически все D-триггеры являются динамическими. При динамическом управлении состоянием триггера используется понятие фронта. Фронтом называют переход от 1 к 0. Подразумевается 2 вида фронта:

- Передний. При этом положении осуществляется переход от 0-1.

- Задним фронтом является переход сигнала от 1 к 0.

Существуют разновидности D устройств с дополнительным входом V. Название этого входа расшифровывается как проверочный. Работает такой элемент с неким замедлением. Оно необходимо для предварительной синхронизации сигнала, с его последующим подтверждением. При этом не играет особой роли, сколько памяти занято в устройстве. Обычные и DV-триггеры предназначены для работы в сложных устройствах с множеством ячеек. Например, в электронных счетчиках эти устройства отвечают его за актуальное значение. При его смене состояние триггера изменяет свой фронт.

Далее приведена таблица истинности и УГО фронтов.

Т-триггер

Триггеры типа T на логических элементах включают в себя многие возможности ранее описанных устройств. Есть модели асинхронного и синхронного типа, динамические и с дополнительным подтверждающим входом.

Асинхронные

При получении положительного сигнала на вход, на выходе получается напряжение в 2 раза выше входного. Такой эффект возможен только при импульсном сигнале, поступающем на T вход. При этом частота поступления по временной шкале не имеет препятствий, а значит сигнал доходит гораздо быстрее. Асинхронные T устройства в состоянии логической 1 на выходе имеют противофазу инверсного выхода.

Синхронные

Эти T-триггеры подобны асинхронным. Исключение состоит в наличие тактового сигнала на входе. Также существует противофаза на инверсном выходе и появление удвоенного напряжения.

Устройство T элементов можно легко отнести к делителям импульсных сигналов. Эти элементы работают только при наличии переднего фронта. Иными словами, осуществляется переход от 0 к 1. Но разница заключается в учете временного интервала между импульсами.

Триггеры типа T часто используются в логических вычислительных процессах. Осуществляется это за счет функции увеличения или снижения напряжения:

- При увеличении частоты на выходе с логической 1, осуществляется запись положительного числа.

- При уменьшении частоты на инверсном выходе при логическом 0, осуществляется запись отрицательного числа.

При учете, сколько памяти необходимо для перехода и деления сигнала, элемент может быть дополнен входом подтверждения. Программирование с использованием T-триггера допускает использование устройства в различных электронных счетчиках без встроенной памяти. Далее дана диаграмма работы устройства.

JK-триггер

Является самым универсальным электронным элементом. В этих устройствах присутствуют:

- Входы «J» и«K» в качестве информационных. При этом «J» — обычный вход «S», а «K» — вход «R».

- «С» — вход динамический.

- «R» и «S» статические.

JK устройство работает по принципу перехода из одного состояния в другое, но с учетом единицы времени. Также существует разность при подаче сигнала на вход синхронизации. Иными словами, если на оба входа JK подать логическую 1, то на его выходах появится прямо противоположное значение. Но при этом устройство не воспримет наличие двух 1 единиц как ошибку.

В зависимости от назначения, в данном триггере может использоваться так называемый фронт (передний или задний). В этом случае устройство считается синхронным, а его состояние определяется актуальным положением логических чисел. При расчете рабочего состояния элемента также учитывается возможность одновременного использования устройства в качестве T или D триггера. В этом случае учитывается параметр временного интервала поступления сигнала, какое напряжение будет получено при выходе и устойчивость состояния элемента. Информатика часто использует этот элемент в качестве универсального устройства контроля состояния устойчивой работы простых логических функций. Далее дана диаграмма работы устройства.

Симметричный

Симметричный триггер относится к особому виду элементов. Он создается на транзисторах и является усилителем постоянного тока двухкаскадного типа. Работает устройство за счет использования транзисторов с полностью идентичными параметрами.

Принцип работы следующий:

- При подаче напряжения на устройство, транзистор VT1 считается открытым. Напряжение его коллектора равняется 0.

- В этот момент транзистор VT2 закрыт. Его коллектор имеет положительное напряжение.

- Для осуществления перехода из одного состояния в другое используется импульс напряжение. Этот импульс создается конденсатором.

- При появлении импульса транзисторы меняют свое состояние.

При смене положения транзисторов создается перепад напряжения, и оно значительно снижается.

В схемах симметричных триггеров основным элементом является система запуска. Она может отличаться по способу управления и месту, с которого поступил пусковой импульс.

- Раздельное управление. Предполагает подачу напряжения на определенный вход триггера. При таком управлении элемент считается RS-триггером.

- Общее или счетное управление. Напряжение подается на общий входной контакт. При таком подключении, устройство схоже по параметрам с Т-триггером.

Место поступления импульса может быть от коллектора или базы транзистора. При таких схемах подключения существует вероятность появления ложного или вторичного сигнала. Он отсекается путем подключения диода.

Основным недостатком симметричных элементов является полная зависимость от времени поступления импульсного сигнала и его длительности. Если длительность недостаточная, импульс не успеет открыть транзистор, а значит не произойдет закрытие второго транзистора.

Такие устройства используются в устройствах учета импульсов, генераторах частоты, переключателях радиоэлектронных цепей.

Заключение

С триггерами в жизни мы сталкиваемся довольно часто, ведь они широко используются в различных сферах. В данной статье было приведено описание и области использования различных разновидностей данного устройства. При ремонте электронного оборудования важно знать: для чего нужен этот элемент, где он используется и по какому принципу работают такие устройства.

Видео по теме

- Алгоритм схемы элемента и таблица истинности

- Виды триггеров

- Логическая схема RS – триггера

- Анализ работы, таблица истинности RS – триггера

1. Алгоритм схемы элемента и таблица

истинности

Триггер – основа устройств оперативного

хранения информации. Наряду с универсальными

логическими элементами И-НЕ, ИЛИ-НЕ триггеры

являются теми “кирпичиками”, которые

составляют фундамент современной электронной

автоматики и цифровой техники.

Триггер – элемент для хранения одного бита

информации. Зная функцию, которую должен

выполнять элемент, напишем словесный алгоритм

схемы триггера.

- Устройство должно “помнить” 0 или 1, причем это

состояние можно прочитать. Значит, должен быть

один выход Q (его состояние и есть хранимый бит) и

второй выход

для обратного значения хранимого бита (часто

необходим, вспомните “обратный код числа”).

Рис.1. - Устройство должно допускать переключение в

другое состояние, с другим значением на выходе,

т.е. должен быть вход. Удобно, если у него два

входа: один для записи единицы S, другой R – для

записи нуля. - Если на входах нет сигналов, т.е. нули, состояние

выхода должно сохраняться. Как? Для сохранности

установленной информации необходима “петля”

(от выхода Q на вход подавать обратно хранящиеся

значение Qстар.), т.е. состояние на выходе Q

зависит от предыдущего его состояния Qстар. Процесс

хранения появляется потому, что сначала элемент

создает сигнал на выходе, и лишь, затем этот

сигнал попадает на вход. - Переключение на хранение другой информации

происходит при подаче короткого сигнала, после

чего на входах опять остаются нули. Итак,

основное состояние триггера – нули на входах.

Построим таблицу истинности элемента по

словесному алгоритму (выход во внимание пока не берем).

Таблица 1.

|

Таблица 1. |

||||||

|

№ |

Входы |

Выход Q |

Примечания |

Итог |

||

|

S |

R |

Qстар. |

||||

|

0 |

0 |

0 |

0 |

0 |

На входы R,S ничего не подается.

Qстар |

Хранение 0 |

|

1 |

0 |

0 |

1 |

1 |

На входы R,S ничего не подается.

Qстар |

Хранение 1 |

|

2 |

0 |

1 |

0 |

0 |

Поданный сигнал на R во время хранения 0 записывает в триггер 0. |

Запись 0 (сброс) |

|

3 |

0 |

1 |

1 |

0 |

Поданный сигнал на R во время хранения 1 записывает в триггер 0. |

|

|

4 |

1 |

0 |

0 |

1 |

Поданный сигнал на S во время хранения 0 записывает в триггер 1. |

Запись 1 (установка) |

|

5 |

1 |

0 |

1 |

1 |

Поданный сигнал на S во время хранения 1 записывает в триггер 1. |

|

|

6 |

1 |

1 |

0 |

Х |

Рассмотренные выше сигналы на входе/выходе достаточны для хранения бита информации. О значениях наборов 6,7 смотри в |

Х- любое состояние |

|

7 |

1 |

1 |

1 |

Х |

2. Виды триггеров

Основная функция триггера — хранение

информации. Но, вместе с тем, за счет

дополнительных цепей управления и особенностей

схематики триггеры получают уникальные

свойства, позволяющие говорить о семействе

интегральных триггеров с целым рядом

дополнительных возможностей по преобразованию

информации.

Доопределение функции Q возможно с помощью

сочетаний наборов 6,7 в таблице 1: 00, 11,

01, 10. Эти четыре варианта доопределения

приводят к четырем основным типам триггеров.

(Таблица 2)

|

Таблица 2. |

||

|

Виды триггеров |

Наборы |

|

|

6 |

7 |

|

| RS- асинхронный триггер | 0 | 0 |

триггер |

1 | 1 |

| E – асинхронный триггер,

RSC-синхронный D-синхронный триггер |

0 | 1 |

| JK -универсальный триггер,

T -счетный |

1 | 0 |

3. Логическая схема RS – триггера

Доопределим логическую функцию Q в таблице

истинности нулевыми значениями.

Запишем CДНФ.

Минимизируем на основе законов алгебры логики:

Для реализации на базисе ИЛИ-НЕ преобразуем

функцию к удобному виду (воспользуемся законами

двойного отрицания и отрицания): .

На схеме второй выход обозначим . (Рис. 2). При

анализе работы триггера убедимся, что это так.

Т.е. на прямом и инверсном выходах сигналы всегда

противоположны.

Можно реализовать функцию на базисе И-НЕ, для

этого преобразуем её к удобному виду:

Полученный вид функции показывает, что

триггер можно собрать на 4-х логических базисных

элементах И-НЕ. Рис.3.

4. Анализ работы, таблица истинности

RS – триггера

Рассмотрим логическую схему RS-триггера на

базисе И-НЕ.

- Пусть подали сигнал только на вход R (S=0, R=1).

- Пусть сигнал только на входе S (S=1, R=0).

- Пусть входных сигналов нет (S=0, R=0).

Логические элементы Э1, Э2 инвертируют сигналы.

В результате на один вход Э3 поступает 1, а на один

вход Э4 – 0. Поскольку на одном из входов Э4 есть 0 ,

независимо от состояния другого входа на его

выходе

обязательно установится 1. Эта единица

передается на вход Э3 и в сочетании =1 порождает на

выходе Э3 Q=0.

Вывод. Если подается сигнал только на вход R

(S=0, R=1),то на прямом выходе триггера нет

сигнала Q=0, а на выходе =1.

Примечание. Обозначение состояния триггера по

договоренности связывается с прямым выходом (Q).

Рассмотренная комбинация входных сигналов

делает на прямом выходе 0, говорят: “триггер

сбрасывается”. Сброс по-английски называется

“Reset”, отсюда вход, появления сигнала на котором

приводит к сбросу триггера, обозначают буквой R.

Логические элементы Э1, Э2 инвертируют сигналы.

В результате на один вход Э3 поступит 0, а на

один из входов Э4 -1. Поскольку на одном из входов

Э3 есть 0, независимо от состояния другого входа

на выходе Q обязательно установится 1. Эта единица

передается на вход Э4 и выход станет равен

нулю.

Вывод. Если сигнал подается только на вход S

(S=1, R=0), то на прямом выходе триггера Q=1, а на

выходе =0.

Примечание. Триггер перейдет в единичное

состояние – “установится” (установка

по-английски “Set”), отсюда вход, появления

сигнала на котором приводит к установки в

триггере 1, обозначают буквой S.

Тогда на один из входов элементов Э3 и Э4 будет

подана 1, и их выходной сигнал будет зависеть от

сигналов на других входах.

=1. Эта единица передается на вход элемента Э3 и

поддерживает нулевое состояние выхода Q (храним

ноль).

Вывод. Это наглядно показывает, что при

отсутствии сигналов на входах триггера

состояние триггера становится устойчивым, а

триггер сохраняет свое “предыдущее” состояние.

- Если сигнал подать на оба входа (S=1, R=1).

На обоих выходах триггера установится 1!!! Такое

состояние является неустойчивым: после снятия

входных сигналов в зависимости от того, какой из

единичных импульсов от Q или “подойдет” быстрее к входам

элементов Э3,Э4: если к Э3, то Q=1, =0, если к Э4, то Q =0,

=1 , т.е. триггер

случайным образом перейдет в одно из своих

устойчивых состояний. Эта комбинация на практике

не используется и является в RS – триггерах

запрещенной.

Проанализировав работу RS-триггера, запишем

таблицу истинности:

|

Таблица 3. |

||||

| Входы | Выходы |

Примечания |

||

| S | R | Q | ||

| 0 | 0 | x | x | Хранение (0 или 1) |

| 0 | 1 | 0 | 1 | запись 0 (сброс) |

| 1 | 0 | 1 | 0 | запись 1 (установки) |

| 1 | 1 | 1 | 1 | запрещено Q |

Историческая справка: В 1918 году советский

ученый М.А. Бонч-Бруевич изобрел ламповый

триггер, а в 1919 году независимо от него такой же

прибор изобрели американцы У. Икклз и

Ф. Джордан.

Мы видим, что триггер обладает замечательным

свойством: после снятия входных сигналов он

сохраняет свое состояние, а значит, может служить

устройством для хранения одного бита информации.